Obsah:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:55.

- Naposledy zmenené 2025-01-23 15:05.

V minulosti som spísal návod, ako postaviť počítač na báze Z80, a obvod som navrhol tak, aby bol čo najjednoduchší, aby ho bolo možné postaviť čo najľahšie. Napísal som aj malý program, ktorý používa rovnakú myšlienku jednoduchosti. Tento dizajn fungoval celkom dobre, ale nebol som s ním úplne spokojný. Začal som prepisovaním programu, ktorý mu umožnil naprogramovať ho za behu. To mi umožnilo otestovať časti kódu bez toho, aby som ho musel venovať EEPROM, čo by zase vyžadovalo preprogramovanie EEPROM. Toto mi neprišlo ako zábavný nápad. Potom som začal premýšľať o pamäťových priestoroch. Ak by som chcel prepojiť kus hardvéru (hlavne IO), kus kódu by potenciálne mohol prekročiť množstvo pamäte, ktoré má systém k dispozícii. Pamätajte si, že návrh používal iba dolný bajt adresovej zbernice a potom spodný bit vysokého bajtu bol použitý na výber medzi priestormi ROM a RAM. To znamenalo, že som mal k dispozícii iba 253 bajtov priestoru. Možno sa pýtate, prečo 253 namiesto 256. Je to preto, že môj nový kód vkladá tri bajty údajov na konci napísaného programu (to bude popísané neskôr, keď som ho upravil tak, aby pracoval na novom dizajne).

n

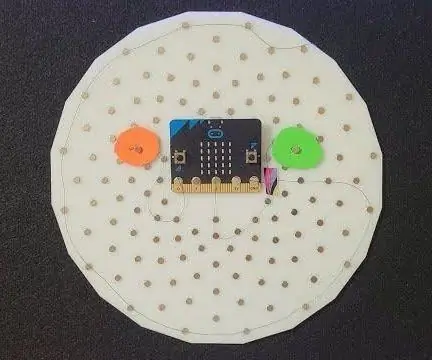

Vrátil som sa k starým schémam, aby som zistil, čo sa ešte deje. Našiel som malú chybičku obvodu výberu pamäte, ktorý zakryjem, keď sa tam dostanem. Zjednodušená verzia: Všetky požiadavky na zápis by v skutočnosti prešli, aj keď sa vždy vložili do pamäte RAM. Pravdepodobne to nebolo dôvod na znepokojenie, ale tentoraz som to chcel urobiť poriadne. A s tým som začal kresliť novú schému. Dva obrázky pripojené k tejto stránke sú pred a za skutočným obvodom. Vyčistil som toľko špagetových rozvodov, nie je to smiešne.

n

Ak budete postupovať podľa môjho pôvodného podania a plánujete nasledovať aj toto, budete ma nenávidieť. Ak začínate odznova, máte šťastie. Jednoducho uchopte diely v zozname (alebo ich ekvivalent) a postupujte podľa nich.

Zásoby:

LM7805 - 5 voltový regulátor Z80 - procesor; mozgy systémuAT28C64B - EEPROM. „Trvalé“úložisko údajov používané pre firmvér počítačaIDT6116SA - SRAM; slúži na ukladanie užívateľského kódu a /alebo všeobecného ukladania dátNE555 - Systémové hodiny74HC374 - Oktálna D -západka s /OE; použitý ako vstupný čip74LS273 - Octal D -Latch with /MR; výstupný čip TLC59211 - čip ovládača LED (používa sa tak, že 74LS273 môže napájať LED diódy, pretože ako taký nie je schopný súčasného výstupu) MC14572 - Jedná sa o čip „Line Driver“, ale zistil som, že je perfektný pre logiku riadenia pamäte. Má 4 meniče a bránu NAND a NOR zabudovanú v 74LS32 - Štvornásobná alebo brána CD4001 - Štvornásobná brána NORCD4040 - 12 stupňový počítadlo zvlnenia; Nakreslený, ale neimplementovaný rozdeľovač hodín (na spustenie systému pri nižších hodinových rýchlostiach) 2 Rezistory 10K Ohm - Jeden sa používa v obvode časovača 555, takže použite akúkoľvek hodnotu, ktorú by ste chceli 4 4 Rezistory 1K Ohm - Jeden sa používa pre Obvod časovača 555, takže použite, čo chcete. Ďalší sa používa na napájanie diód LED, takže ho tiež zmeňte, ak chcete: 8x330 ohm odporová zbernica 8x10k ohm odporová zbernica 11 diód LED - tri sa používajú na stav systému a ďalších osem je výstupov. Pre 8 som použil stĺpcový graf (HDSP -4836) 4 kondenzátory - Dva sú použité LM7805; 0,22uF a 0,1uF. Jeden je pre časovač 555, takže používajte to, čo považujete za správne. Posledný slúži na resetovanie pri zapnutí; 100uF2 N. O. Tlačidlá - jedno slúži na vstup, druhé na resetovanie 8 prepínačov SPST DIP - vstup údajov; Použil som Piano Key styleWire. Veľa a veľa drôtu

n

POZNÁMKA: Verzia MC14572 cez diery je zastaraná, ale verzia SMD je stále aktívna (dokonca ani stav „nie pre nový dizajn“), takže na jej použitie budete možno musieť kúpiť dosku s plošnými spojmi. Namiesto MC14572 je možné použiť druhý 74LS32 (pozri schému „obvodu výberu pamäte“predchádzajúceho článku)

Krok 1: Rýchly prehľad zmien + schémy

Ako čítať schémy: Šípka nasmerovaná na čip je vstup: Vstup> -Šípka smerujúca od čipu je výstup: Výstup <-Busy používajú namiesto šípky riadok: Bus |-

n

Väčšina žetónov bola nakreslená s presnými vývodmi. Malý pokles bol čerpaný z týchto čipov. Väčšina čipov má tiež čísla PIN a štítky. Môžu byť trochu ťažko čitateľné. Moja ceruzka začínala byť matná.

n

Pokiaľ ide o zapojenie obvodov, rozloženie nového dizajnu sa od pôvodného väčšinou nemení. Pripojil som spodný nibble horného bajtu adresy k pamätiam a potom som použil nízky bit horného nibble (A12) na výber RAM/ROM. To znamenalo, že ROM priestor prešiel od 0000-00FF do 0000-0FFF. Priestor barana prešiel z 0100-01FF na 1000-1FFF. Tiež som vymenil logiku ovládania pamäte za lepší dizajn a pridal dve nové stavové diódy LED (a nejakú logiku lepidla). Nakreslil som (ale nepripojil) obvod rozdeľovača hodín. Mala plniť dve funkcie. Zjavnou funkciou je rozdeliť hodinovú frekvenciu nadol. Druhá funkcia je na účely PWM (Pulse Width Modulation), pretože 555 negeneruje vlny s 50% pracovnými cyklami. V tomto obvode na tom nezáleží, ale ak by ste chceli použiť hodiny na napájanie niektorých diód LED, určite si všimnete efekty (jedna (sada) diód LED bude slabšia ako druhá). Celý zvyšok obvodov je v podstate nezmenený.

Krok 2: CPU, pamäť a ovládanie pamäte

Toto je časť, kde ma čitatelia mojej predchádzajúcej verzie nenávidia. V pôvodnom prevedení som len hodil diely na dosku na miesto, ktoré vyzeralo, že budú mať malý problém s zapojením. Výsledok vyzeral, že na neho niekto vysypal tanier špagiet a bol ako „drôty!“Chcel som to trochu vyčistiť, a tak som začal roztrhnutím všetkého okrem CPU, RAM a ROM. Vytiahol som takmer celý vstupný obvod, výstupný obvod a logiku lepidla. Skoro ma to bolelo, ale bolo to nevyhnutné. Všetky dátové pripojenia som nechal nedotknuté a dolný bajt adresovej zbernice. Potom som pripojil ďalšie štyri bity adresovej zbernice (A8-A11) k čipu ROM. Tentoraz som sa postaral o to, aby som obišiel čip, aby som sa ľahšie vytiahol na preprogramovanie. Tiež som preskočil pripojenia adries na čip RAM.

n

Keď som z toho vyšiel, musel som teraz zapojiť logiku riadenia pamäte. V pôvodnej schéme som pripojil linku procesora /MREQ priamo k /CE k obom pamäťovým čipom, potom som zapojil /WR do pamäte RAM /WE. Potom som logicky spojil procesorové jednotky /RD a /MREQ a tiež A9. V zásade bol nastavený tak, aby všetky požiadavky na pamäť aktivovali RAM aj ROM, ale na výber, ktorý z čipov /OE bol vybraný, bol použitý A9. To bolo v poriadku a to všetko preto, že čipy zostali neaktívne, kým nebola zadaná požiadavka na pamäť a potom bol počas požiadavky na čítanie aktívny iba jeden /OE. To zabránilo presluchu, ale prinieslo to nepríjemnú nuanciu. Pretože A9 slúžil iba na určenie, z ktorého čipu sa prenášajú údaje, a pretože procesor mal priamy prístup na pin RAM /WE, všetky požiadavky na zápis by prešli. To bolo v poriadku pre ROM, pretože jeho režim zápisu je inhibovaný viazaním /WE priamo na 5V napájanie. RAM by však bola zapísaná bez ohľadu na A9. To znamenalo, že pokus o zápis na miesto v priestore ROM zapíše na rovnaké miesto v priestore RAM.

n

Jedným z riešení by bolo prepojenie riadiacej logiky tak, aby mal procesor priamy prístup k pinom /OE a /WE čipov a potom pomocou MREQ a A12 zvoliť, ktoré čipy /CE boli riadené. Išiel som s touto myšlienkou, ale namiesto použitia štyroch brán NOR a invertora, ako bol pôvodný dizajn, som našiel nepríjemný malý čip, ktorý bol na túto úlohu perfektný. Musel som vytvoriť obvod, ktorý používal iba logické brány dostupné v čipe, ale bolo to dosť jednoduché. A12 sa napája priamo na bránu NAND a bránu NOR. /MREQ sa privádza do brány NOR a jej kompliment sa privádza do brány NAND. Brána NAND sa používa na pohon /CE pre RAM a výstup NOR sa invertuje a používa sa na pohon ROM /CE. Vďaka tomu musí byť /MREQ nízky pred výberom jedného z čipov a potom A12 zvolí, ktorý z nich bude vybraný. S týmto nastavením teraz žiadne požiadavky na zápis do pamäte ROM nič neurobia. Šetrí tiež energiu, pretože namiesto oboch je aktívny iba jeden čip. Čo sa týka samotného logického čipu, vnútri máme ešte dva nepoužívané meniče. Jeden si zvykne neskôr, ale dostaneme sa tam, keď sa tam dostaneme.

Krok 3: LED diódy stavu systému

Predtým, ako som začal s týmto projektom, pokúšal som sa prepojiť s určitým integrovaným obvodom, ale mal som s tým problémy. Nie som si istý, čo sa deje, a tak som použil sondu LED na montáž na panel (jedna z tých zostáv, v ktorých je zabudovaný odpor). Vďaka tomu som dostal nostalgický nápad, ktorý sa používa dodnes: stavové diódy LED informovali o tom, či sa z pamäte číta alebo do nej zapisuje. Mala byť použitá v spojení so vstupnou LED, ktorú som už mal. Vstupná dióda LED bola pripojená k generátoru signálu /WAIT, aby nám naznačila, že systém dobre čaká na vstup (dostanem sa tam, nebojte sa). Uvažoval som o pridaní LED diódy na indikáciu zápisu IO, ale prišiel som na to, že zmena výstupných LED diód by už bola toho skvelým indikátorom. Keď o tom premýšľam, možno to ešte pridám. Považujem však za užitočné vedieť, či sa pamäť číta alebo zapisuje. Je to však užitočné pre ladenie programu. V skutočnosti som to vo veľkej miere používal pri pokuse o spustenie programu: „Prečo to zapisuje do pamäte? To sa ešte nemalo robiť!"

n

Na ovládanie týchto LED som použil bránu NOR quad. Použil som všetky brány. Na generovanie stavových signálov boli použité iba dva, ale čip nemá výkonové možnosti na skutočné napájanie diód LED. Sú schopné potopiť toľko energie, takže som použil ďalšie dve brány NOR ako invertory a ako také som zapojil LED diódy. Pretože jedna LED dióda slúži na označenie čítania a druhá na zápis a požiadavka na čítanie a zápis sa nevyskytne súčasne, dokázal som sa vyhnúť použitiu iba jedného rezistora na obe LED diódy. Pokiaľ ide o signály, ktoré som potreboval dekódovať, bolo to tiež dosť jednoduché. Chcel som, aby boli indikované všetky požiadavky na čítanie pamäte, takže prvá brána NOR mala na svojich vstupoch /MREQ a /RD. Stav zápisu bol trochu zložitejší, ale rovnako ľahký. Stále som používal /MREQ ako jeden vstup, ale použitie /WR ako druhého by spôsobilo menšiu nuanciu, ktorej som sa chcel vyhnúť. Znamenalo by to VŠETKY žiadosti o zápis. Chcel som len tie, ktoré skutočne prešli. Ako by som to teda urobil? Pamätáte si, ako mám nastavený systém, aby sa dala zapísať iba pamäť RAM? Ako ďalší vstup do brány NOR som použil RAM /CE. To znamená, že dióda LED sa rozsvieti iba vtedy, keď je vybratá pamäť RAM a prebieha požiadavka na zápis. Pokiaľ ide o farbu LED, ako indikátor čítania som vybral oranžovú (našiel som však iba žlté) a ako indikátor zápisu červenú.

Krok 4: Vstup a výstup

V predchádzajúcom kroku ste si mohli všimnúť, že som na dosku už pridal niektoré zo zvyšných komponentov. Rezervoval som si priestor, aby som omylom neumiestnil káble tam, kde by som chcel komponent (teda musel by som nájsť nové umiestnenie pre tento komponent). Možno ste si tiež všimli, že som nechal vstupné spínače na mieste a zapojil ich až k napájacej lište. Rozhodol som sa, že pôvodné miesto je perfektné miesto, a rozhodol som sa umiestniť výstupné diódy LED v blízkosti (vyššie). Vpravo od panelového displeja je západka vstupu. Nad tým je výstupná západka a naľavo od nej je ovládač LED. Začal som pripojením displeja k ovládaču, pretože to bolo najľahšie. Potom som prepínače pripojil na vstupnú stranu vstupnej západky. Ďalej som pripojil výstupnú stranu výstupnej západky k ovládaču LED. Môže sa to zdať ako trápny príkaz na zapojenie týchto káblov, ale malo to svoj dôvod. Vstup výstupnej západky mal byť prepojený s dátovou zbernicou a rovnako aj výstup vstupnej západky. Cieľom bolo prepojiť výstupy vstupnej západky so vstupmi výstupnej západky, čo som urobil. Potom som už len musel dostať ten neporiadok prepojený s dátovou zbernicou. Nezáležalo na tom, kam tieto spojenia fyzicky smerovali, pretože všetky boli elektricky prepojené. Počítač je teraz takmer hotový.

Krok 5: Reset a dokončenie vstupu a výstupu

Ospravedlňujeme sa, pre tento krok nie sú žiadne fotografie. Obrázky nájdete v predchádzajúcom kroku.

n

Možno ste si na poslednom obrázku predchádzajúceho kroku všimli, že som mal nainštalované zelené tlačidlo a ďalší logický čip. Čip je brána OR. Na generovanie signálu /WAIT sa používajú dve brány. Jeden generuje signál pomocou OR-ing /IORQ a /RD z procesora. Výstup sa zavedie do druhej brány, kde sa znova dostane k tlačidlu ALEBO. Tlačidlo privádza vstup brány vysoko, čím zvyšuje výstup. Tento výstup je privádzaný na pin procesora /WAIT. Rezistor nie je stlačený, ale drží vstup nízko. Pôvodne som používal 10K odpor, ale LS32 v skutočnosti privádzal na vstup napätie. Rezistor neklesol dostatočne nízko a musel som ho nahradiť 1K. V každom prípade ide o to, že keď je odoslaná požiadavka na čítanie IO, prvá a druhá brána OR oznámi procesoru, aby počkal. Akonáhle nastavíte prepínače vstupu na čokoľvek, čo chcete, stlačíte tlačidlo a procesor sa dostane z stavu čakania. Zelená dióda LED „vstupu“, ako som ju v predchádzajúcom kroku nazval, je zapojená tak, že keď kolík /WAIT zhasne, rozsvieti sa.

n

Ale ešte sme neskončili. Vstupný klopný obvod potrebuje signál, ktorý by mu oznámil, že vstup údajov je platný, a mal by byť vložený do CPU. Tento kolík hodín je aktívny vysoko. Predtým sme ho len pripojili k tlačidlu. Toto je stále platná možnosť, ale tentokrát som sa rozhodol dať to na rovnaký výstup ako druhá brána OR. Tento IC má tiež pin OE, ktorý je potrebné poháňať. Ak by sa držal vysoko, nikdy by nevložil údaje do zbernice. Ak by sa držal nízko, vždy by to riadilo autobus. Na vyriešenie tohto problému som jednoducho použil tretiu bránu OR. Vstupy sú /IORQ a /RD a výstup smeruje priamo do /OE západky.

n

Výstupná západka tiež potrebuje na pohon hodinový kolík. Opäť je aktívny vysoko. V mojej schéme som nakreslil štvrtú bránu OR priamo poháňajúcu kolík pomocou /IORQ a /WR. To znamenalo, že hodinový kolík bude držaný vysoko, kým nebude podaná žiadosť o zápis, potom pôjde opäť dole a potom vysoko. To by pravdepodobne bolo v poriadku, pretože na dátovej zbernici by boli stále platné údaje bezprostredne po pokuse o zápis, ale z technického hľadiska to bol odpad. Túto chybu som si všimol až potom, čo som urobil posledné obrázky, ale roztrhol som toto spojenie a potom som napájal výstup brány OR do jedného z nepoužitých meničov z logiky riadenia pamäte a potom som pripojil jeho výstup k hodinovému kolíku. Tiež som opravil schému a našiel som ďalšiu chybu, ktorú som urobil. Tiež som to opravil.

n

Keď som to všetko konečne urobil, čakalo ma veľmi malé množstvo práce: resetovací obvod. Na dosku som pridal tlačidlo a pomocou 10K rezistora držal jednu stranu vysoko. Druhá strana ide priamo na zem. Najvyššou stranou je výstup /RESET, ktorý prešiel na každý čip pinom /RESET (západka CPU a výstupu). Aby sa dosiahol reset pri zapnutí, pridal som na výstup /RESET kondenzátor. Ide o to, že odpor s veľkými hodnotami by spôsobil, že relatívne veľký kondenzátor sa bude nabíjať pomaly a pri určitom počte hodinových cyklov (CPU potrebuje štyri taktové cykly) držať piny /RESET nízko. Už asi tušíte, aká je negatívna stránka tohto obvodu. Je to rovnaké negatívne ako predchádzajúca verzia, pretože je to ten istý obvod. Keď je tlačidlo stlačené, kondenzátor je v podstate skratovaný cez tlačidlo. To je zlé pre uzáver aj tlačidlo, takže ak chcete, aby bola vaša zostava trochu trvalejšia, možno by ste ju chceli prepracovať. Myslel som na ďalší časovač 555 nastavený v monostabilnom režime. Ale s tým je obvod počítača teraz dokončený. Jéj. Teraz to potrebuje naprogramovať.

Krok 6: Programovanie

Programovanie tejto veci bolo nočnou morou. Postavil som programátor Arduino EEPROM. Nefungovalo to Postavil som ďalší podľa návrhu a kódovania niekoho iného. Stále nefungovalo. Vrátil som sa k osvedčenej metóde ručného ručného nastavovania adries a dátových bajtov. Nejako som to pokazil. Skúsil som to znova a stále som to zle pochopil. Vrátil som sa ešte raz a zistil som, že je vypnutý o jeden bajt, takže som to opravil a nakoniec to fungovalo, vďaka bohu.

n

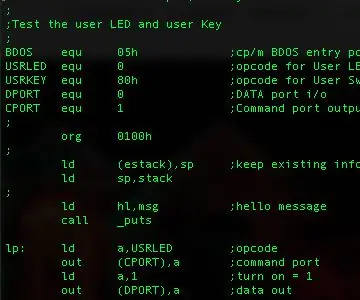

Pokiaľ ide o skutočný program, vyzerá to, že je super zložitý a ťažko sa sleduje, ale nie je. Je to vlastne celkom jednoduché. Polovica z nich kopíruje čísla. Druhá polovica je rozdelená medzi 16-bitovú matematiku, podmienené skoky a ešte viac čísel na kopírovanie. Dovoľte mi, aby som to prešiel a povedal vám, ako to funguje.

n

Inicializácia len nastaví niektoré hodnoty registra na použitie v programe. Programová slučka je o niečo zložitejšia, ale nie celkom. Najprv prijíma vstup do registra A na porte 00. Potom sa register E zapíše do pamäte. Register E obsahuje v prvých dvoch slučkách nevyžiadané údaje, takže sa ich pokúšame zapísať do posledných dvoch bajtov priestoru ROM, pretože v skutočnosti nebudú zapísané; ukazovateľ adresy (IY) sa potom zvýši. Hodnota uložená v D sa potom presunie do E a zapíše sa ďalej. A sa potom zavedie do D a L a E sa skopíruje do H. HL je miesto, kde dochádza k porovnaniu hodnôt odčítaním a kontrolou ZF (nulový príznak). Prvá porovnávaná hodnota je uložená v registroch B a C. S B a C sa zaobchádza ako s jediným 16-bitovým registrom BC. Ak sú hodnoty rovnaké, program skočí priamo do priestoru RAM, kde sa predpokladá, že sa nachádza užívateľský kód. Ak kód v BC nie je zhodný, potom sa do HL znova načítajú počiatočné hodnoty z D a E a znova sa porovnajú s hodnotou v SP rovnakým spôsobom, akým sa porovnával s BC. Ak je to zhoda, má to rovnaký výsledok, ale tri ďalšie bajty sa zapíšu do pamäte. Bajty sú kód, ktorý spôsobuje, že CPU preskočí späť na úplný začiatok programu (reset softvéru). Ak však druhé porovnanie nezodpovedá, program sa vráti tam, kde od používateľa získa hodnotu.

n

LD SP, EDBFH; exe kód (pridáva skok)

n

LD IY, FFEH; počiatočný ukazovateľ pamäte na ukladanie kódu

n

LD BC, EDC3H; exe kód (žiadna slučka)

n

slučka; assembler, aby sme nemuseli vedieť, kde v pamäti je táto časť

n

IN A, (00H); získať údaje o programe

n

LD (IY+00H), E; E obsahuje kód, ktorý sa má uložiť

n

INC IY; prejsť na ďalšie miesto v pamäti

n

LD E, D; Dd do E

n

LD D, A; ld A do D

n

LD H, E; ld E do H

n

LD L, D; ld D do L.

n

ALEBO A; resetovať vlajku prenosu

n

SBC HL, BC; vráti 0, ak bol zadaný exe kód 2

n

JP Z, 1000H; ak je to tak, skočte na program a spustite ho

n

LD H, E; v opačnom prípade ich obnovte na správne hodnoty

n

LD L, D

n

ALEBO A; prvý odčítanie môže mať nastavený príznak prenosu. Vymaž to

n

SBC HL, SP; vráti 0, ak bol zadaný exe kód 1

n

JP NZ, slučka; ak nie, zopakujte postup (začínajúc získaním hodnoty)

n

LD (IY+00H), C3H; v opačnom prípade zadajte na konci užívateľského programu skokový kód

n

LD (IY+01H), 00H; jump v zásade funguje ako reset softvéru

n

LD (IY+02H), 00H; je to úplný reset v prípade úpravy registrov

n

JP 1000H; skočte na a spustite užívateľský program

Odporúča:

Zosilňovač reproduktorov počítača: 6 krokov (s obrázkami)

PC reproduktorový zosilňovač: Jedná sa o malý výkonový (menej ako 10 W) tranzistorový zosilňovač využívajúci LM386 a TIP41/42. Aj keď výstupný výkon nie je príliš pôsobivý, napriek tomu môže dobre slúžiť ako zosilňovač pre reproduktor PC a prehrávač MP3. Keď žijete v zabalenom zariadení spoločný byt, ha

Zostavenie počítača 1 KCTC, druhá relácia: 14 krokov

Počítačová zostava 1, 2. zasadnutie KCTC: Na dokončenie zostavy budete potrebovať nasledujúce diely: 1) základná doska 2) procesor 3) chladič + ventilátor 4) RAM5) počítačová skrinka 6) pevný disk 7) napájací zdroj 8) grafická karta

Z80-mbc2 Kód LED blesku Z80 pre používateľa: 3 kroky

Z80-mbc2 Z80 Code Flash User LED: Toto je príklad užívateľského LED programu napísaného v assembleri Z80 pre počítač z80-mbc2. Urobil som pre mňa test a revíziu, toto je môj prvý program Z80 viac ako 35 rokov. Užite si to

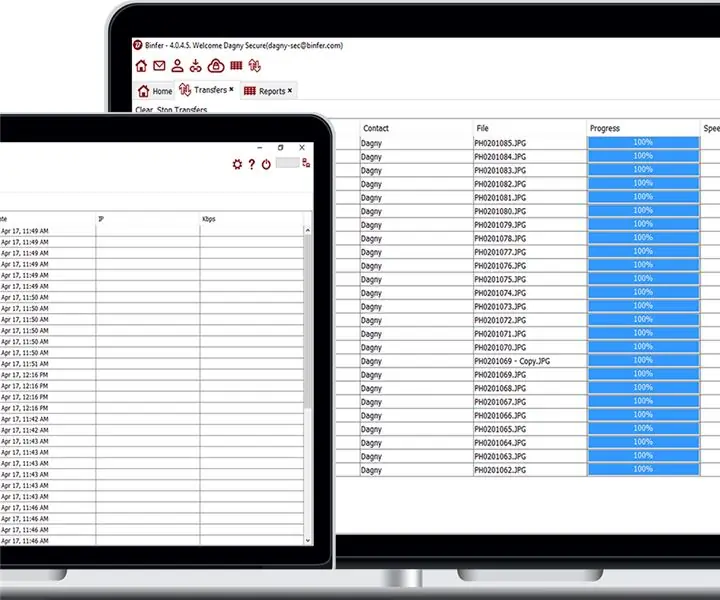

Ako odosielať veľké súbory z počítača do počítača: 6 krokov

Ako odosielať veľké súbory z počítača do počítača: S pokrokom technológie sa veľkosť súborov stále zvyšuje. Ak sa venujete kreatívnemu remeslu, ako je návrhárstvo alebo modelovanie, alebo len fandíte, prenos veľkých súborov môže byť problém. Väčšina e -mailových služieb obmedzuje maximálne veľkosti príloh na približne 25

Zrýchlenie prenosného počítača / počítača: 8 krokov (s obrázkami)

Zrýchlite prenosný počítač/počítač: SLEDUJTE NÁS NA NAŠICH WEBOVÝCH STRÁNKACH:- http://www.creativitybuzz.org/ Dobrý deň, priatelia, tu vám ukážem, ako doma zrýchliť prenosný počítač alebo počítač. Rýchlosť prenosného počítača sa môže zvýšiť nainštalovaním jednotky SSD pevného disku