Obsah:

- Krok 1: Fáza opätovného zaujatosti

- Krok 2: Rezistor snímajúci prúd

- Krok 3: Zosilňovač transvodivosti

- Krok 4: Zosilňovač prístrojov

- Krok 5: Vstupná fáza a kalibrácia

- Krok 6: Pokročilé veci: Spektrálny únik (DC)

- Krok 7: Pokročilé veci: Spektrálny únik (AC)

- Krok 8: Pokročilé veci: teoretický faktor zisku

- Krok 9: Pokročilé veci: posun PA

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:58.

- Naposledy zmenené 2025-06-01 06:10.

Mal som záujem o výrobu bioimpedančného analyzátora na meranie zloženia tela a moje náhodné vyhľadávania stále nachádzali návrh z triedy Biomedicínskych prístrojov z roku 2015 na Vanderbilt University. Dizajn som prepracoval a mierne vylepšil. Rád by som sa s vami podelil o svoje zistenia. Ak vám niečo nie je jasné, vezmite si z tohto „sprievodcu“, čo môžete použiť. Navrhnite vylepšenia. Možno niekedy napíšem svoje myšlienky súdržnejšie, ale zatiaľ dúfam, že môžete použiť to, čo tu vidíte. (Ak si myslíte, že by ste to mohli napísať a zlepšiť, ste vítaní.)

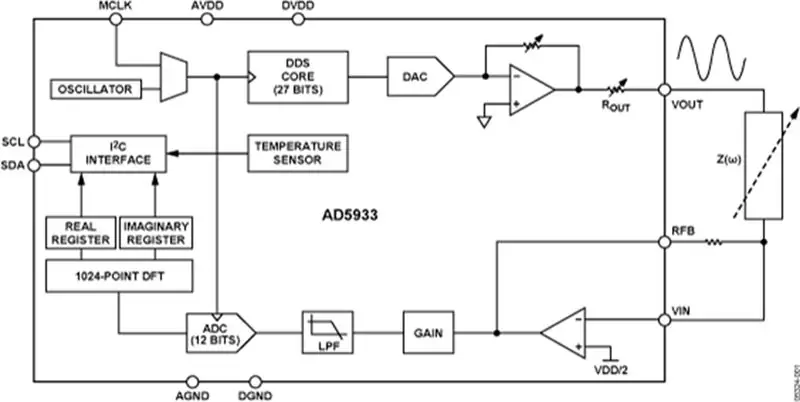

Macko

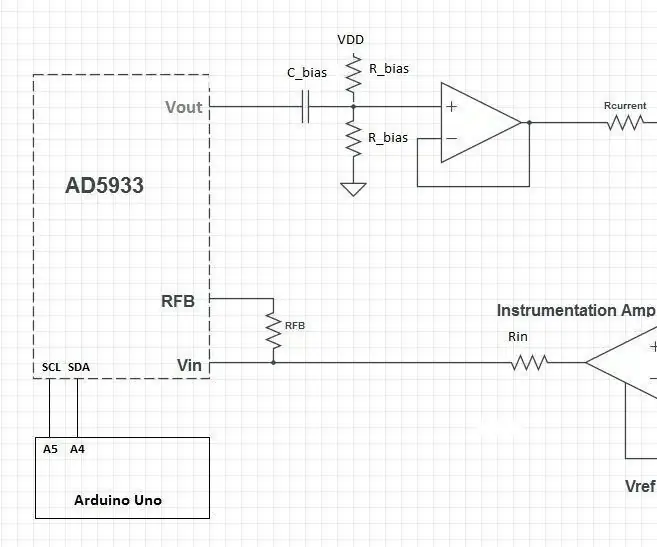

Tento dizajn pozostáva z čipu AD5933 a vlastného analógového klientskeho rozhrania (AFE) na prepojenie AD5933 s telom. AD5933 potom vykoná meranie a výsledky potom môže spracovať mikrokontrolér (napr. Arduino).

Ak plánujete používať Arduino ako zdroj napájania, uistite sa, že operačné a prístrojové zosilňovače (operačné zosilňovače a zosilňovače) podporujú takzvané napätia „jedného zdroja“a majú špecifikácie rail-to-rail.

(V nasledujúcom texte budem používať napájací zdroj (z Arduina) 5 V a nastavenie rozsahu 1 na AD5933.)

Krok 1: Fáza opätovného zaujatosti

Prvá časť AFE je fázou predpätia. Signál výstupného napätia nie je vycentrovaný v strede rozsahu napájacieho napätia (VDD/2). Toto je napravené použitím kondenzátora na zablokovanie jednosmernej časti signálu a jeho odoslaním cez rozdeľovač napätia na pridanie jednosmerného offsetu späť do signálu.

Dva odpory predpätia môžu mať akúkoľvek hodnotu, pokiaľ sú rovnaké. Špecifická hodnota stropu tiež nie je dôležitá.

Fáza opätovného vychýlenia funguje ako hornopriepustný filter, a preto má medznú frekvenciu:

f_c = 1 / (2 * pi * (0,5 * R) * C)

Zaistite, aby bola medzná frekvencia o niekoľko desaťročí nižšia ako minimálna frekvencia, ktorú plánujete používať. Ak plánujete vo svojej aplikácii používať 1 kHz, mali by ste zvoliť hodnoty čiapky a odporu, ktoré vám poskytnú medznú frekvenciu rádovo 1 až 10 Hz.

Poslednou časťou tejto fázy je operačný zosilňovač nastavený ako sledovateľ napätia. To má zaistiť, aby hodnoty odporu nerušili v ďalšej fáze

Krok 2: Rezistor snímajúci prúd

Prvá časť ďalšej etapy je odpor snímajúci prúd. Prúd cez tento odpor bude rovnaký ako prúd, ktorý sa zosilňovač pokúsi udržať v tele. Uistite sa, že prúd vyhovuje bezpečnostným normám IEC6060-1*:

Telo má pod frekvenciami 1 kHz maximálne 10 mikroAmpérov (RMS). Pri frekvenciách nad 1kHz poskytuje maximálny povolený prúd nasledujúca rovnica:

Maximálny striedavý prúd <(minimálna frekvencia v kHz) * 10 mikroAmpérov (RMS)

Vzťah medzi vrcholovou amplitúdou signálu AC a jeho hodnotou RMS je: Peak = sqrt (2) * RMS. (10 microAmps RMS zodpovedá špičkovej amplitúde 14 mikroAmps)

Pomocou Ohmovho zákona o odpore môžeme vypočítať hodnotu odporu, ktorá bude vyhovovať bezpečnostnému štandardu. Používame budiace napätie z AD5933 a maximálnu hodnotu prúdu:

U = R * I => R = U / I

Napr. pomocou nastavenia rozsahu 1 Upeak = 3V / 2 = 1,5V (alebo 1V @3,3V)

Použitím špičkovej hodnoty 14 mikroAmp zhora dostanem hodnotu rezistora najmenej 107 kOhms

Referencie:

* Analógové zariadenia: „Bioimpedančný obvodový obvod pre systémy nosené na tele“

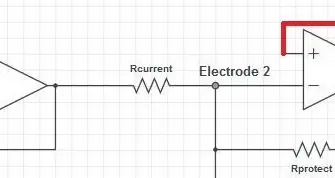

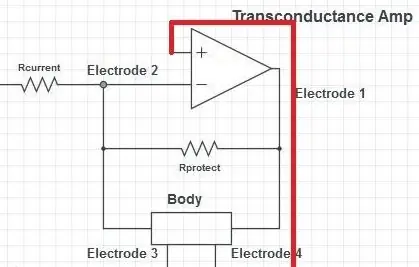

Krok 3: Zosilňovač transvodivosti

Za prúdovým snímacím odporom je operačný zosilňovač v konfigurácii so zápornou spätnou väzbou. Ide o takzvané nastavenie Load-in-the-Loop. Kladný vstupný terminál operačného zosilňovača je pripojený k napätiu VDD/2. Operačný zosilňovač sa teraz pokúsi nastaviť svoj výstup v opačnom smere ako budiaci signál tak, aby napätie na zápornom termináli bolo rovnaké ako VDD/2. To spôsobí potenciál hojdačky tlačením a ťahaním prúdu cez telo.

Prúd odobratý zo záporného pólu operačného zosilňovača je prakticky nulový. Všetok prúd cez odpor snímajúci prúd preto musí pretekať telom. Toto je mechanizmus, ktorý robí z tohto nastavenia zosilňovač transvodivosti (nazývaný tiež zdroj prúdu s riadeným napätím, VCCS).

Operačný zosilňovač môže udržiavať prúd iba vtedy, ak impedancia tela nie je príliš vysoká. V opačnom prípade by výstup operačného zosilňovača dosiahol maximálnu hodnotu pri napájacom napätí (0 alebo 5 V). Maximálne rozpätie napätia, ktoré je možné udržať, je VDD/2 + Upeak (2,5 + 1,5 V = 4 V pri napájaní 5 V). Okraje napätia operačného zosilňovača by sa mali odpočítať od tejto hodnoty, ale ak má operačný zosilňovač špecifikácie rail-to-rail, bolo by to len malé množstvo. Maximálna impedancia, ktorú môže operačný zosilňovač poháňať, je preto:

Z <(VDD / 2 + Upeak) / Imax

(V mojom nastavení Z <4V / 14 mikroAmps = 285 kOhms praje veľa na pokrytie rozsahu impedancie tela)

Ochranný odpor má v porovnaní s telom veľmi veľkú hodnotu (1-1,5 MOhms) (približne 100kOhms) a pri všetkých bežných operáciách z neho nebude čerpať žiadny znateľný prúd a v impedancii paralelného pripojenia dominuje impedancia telesa. Ak by impedancia tela mala stúpať (napr. Uvoľnenie podložiek), prúd môže potom prechádzať cez odpor a maximálne napätie z operačného zosilňovača by v doštičkách nevytváralo nepríjemné napätie.

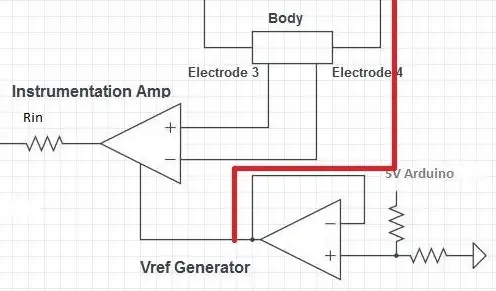

Krok 4: Zosilňovač prístrojov

Ďalšou fázou je prístrojový zosilňovač (in-amp), ktorý meria napätie v celom tele. Napätie v celom tele osciluje okolo 0V, ale AD5933 potrebuje, aby bolo vstupné napätie v kladnom rozsahu. In-amp preto pridáva k meranému napäťovému signálu DC offset VDD/2.

Referencia VDD/2 je generovaná deličom napätia. Je možné použiť rezistor s ľubovoľnou hodnotou, pokiaľ sú rovnaké. Delič napätia je oddelený od impedancie zvyšku obvodov sledovačom napätia. Výstup sledovača napätia potom môže byť presmerovaný do zosilňovača in-amp aj trans-vodivého zosilňovača.

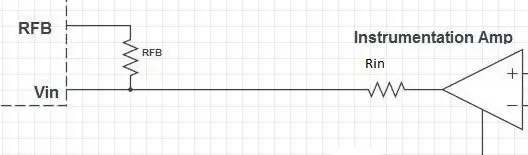

Krok 5: Vstupná fáza a kalibrácia

Vstupný stupeň AD5933 obsahuje operačný zosilňovač v konfigurácii so negatívnou spätnou väzbou. Existujú dva odpory: jeden v sérii (Rin) a jeden paralelne (RFB). Zisk operačného zosilňovača je daný hodnotou

A = - RFB / Rin

Zisky vstupného operačného zosilňovača a zosilňovača (a PGA) musia zaistiť, aby signál prichádzajúci do ADC AD5933 bol vždy v rozsahu 0 V a VDD.

(Používam hodnoty zosilňovača a odporu rezistora, ktoré dajú približne A = 0,5)

Vnútri AD5933 ADC prevedie napäťový signál na a na digitálny signál. Rozsah napätia od 0V do VDD sa prevedie na digitálny rozsah 0-128 (2^7). (Dokumentácia v tomto nie je jasná, ale podrobné skúmanie pozemkov v [1] a niektoré experimenty z mojej strany to potvrdzujú.)

Vnútri modulu DFT je ďalšie škálovanie 256 (1024/4, pozri [1]) predtým, ako je výsledok uložený do skutočného a imaginárneho registra.

Sledovaním napäťového signálu cez AFE do ADC a pomocou vyššie uvedených faktorov stupnice je možné odhadnúť faktor zisku:

g = (VDD * Rcurrent * Rin) / (256 * PGA * Upeak * RFB * 2^7)

môže byť ešte potrebná určitá kalibrácia, takže vezmite do úvahy niektoré efekty, ktoré nie sú súčasťou tohto matematického modelu, preto zmerajte skutočnú hodnotu zisku meraním komponentov známej impedancie, ako sú odpory. (g = Z / mag, pozri nižšie)

Impedanciu je teraz možné vypočítať podľa

Z = g * mag

mag = sqrt (skutočný^2 + imaginárny^2)

PA = arctan2 (skutočný, imaginárny) - deltaPA

PA je pravdepodobne potrebné kalibrovať, pretože v AD5933 existuje systematický fázový posun ako funkcia frekvencie. deltaPA bude pravdepodobne nejaká lineárna funkcia frekvencie.

Odpor a reaktanciu je teraz možné vypočítať pomocou

R = Z * cos (PA)

X = Z * sin (PA)

Literatúra: [1] Leonid Matsiev, „Zlepšenie výkonu a univerzálnosti systémov založených na jednofrekvenčných detektoroch DFT, ako sú AD5933“, Electronics 2015, 4, 1-34; doi: 10,3390/elektronika4010001

Krok 6: Pokročilé veci: Spektrálny únik (DC)

Signál, ktorý vložíme do AD5933, je napätie/prúd ako funkcia času, ale naším hlavným záujmom je impedancia ako funkcia frekvencie. Na konverziu medzi časovou a frekvenčnou doménou potrebujeme Fourierovu transformáciu signálu časovej domény. AD5933 má vstavaný modul diskrétnej Fourierovej transformácie (DFT). Pri nízkych frekvenciách (pod približne 10 kHz) je tvorba DFT ovplyvnená aliasingom a spektrálnymi únikmi. V [1] prechádza matematikou, ako opraviť spektrálny únik. Podstatou toho je vypočítať päť (plus dve) konštanty pre každý frekvenčný krok v cykle. To sa dá ľahko vykonať napr. softvérovým softvérom Arduino.

Únik sa dodáva v dvoch formách: únik jednosmerného prúdu, ktorý má v prírode aditívny charakter, a únik striedavého prúdu, ktorý má multiplikačný charakter.

Únik jednosmerného prúdu pochádza zo skutočnosti, že napäťový signál v ADC neosciluje okolo 0 V, ale okolo VDD/2. Úroveň DC VDD/2 by mala zodpovedať digitálnej hodnote DC približne 64 (označená delta v [1]).

Kroky na opravu spektrálneho úniku DC:

1) Vypočítajte faktor obálky E pre aktuálnu frekvenciu.

2) Vypočítajte dva faktory zisku GI (skutočné) a GQ (imaginárne)

3) Od hodnoty skutočného registra odpočítajte delta * GI a delta * GQ od hodnoty imaginárneho registra

Referencie:

[1] Leonid Matsiev, „Zlepšenie výkonu a univerzálnosti systémov založených na

Jednofrekvenčné DFT detektory ako AD5933 , Electronics 2015, 4, 1-34; doi: 10,3390/elektronika4010001

[2] Konrad Chabowski, Tomasz Piasecki, Andrzej Dzierka, Karol Nitsch, „jednoduchý merač impedancie širokého frekvenčného rozsahu založený na integrovanom obvode AD5933“, Metrol. Merať Syst., Zv. XXII (2015), č. 1, s. 13-24.

Krok 7: Pokročilé veci: Spektrálny únik (AC)

Rovnako ako únik jednosmerného prúdu, aj únik striedavého prúdu je možné matematicky opraviť. V [1] sa odpor a reaktancia nazývajú A*cos (phi) a A*sin (phi), kde A zodpovedá veľkosti impedancie a phi zodpovedá fázovému uhlu (PA).

Kroky na opravu spektrálneho úniku striedavého prúdu:

1) Vypočítajte faktor obálky E (nie je rovnaký ako pre DC) pre aktuálnu frekvenciu.

2) Vypočítajte tri faktory a, b a d. (približné hodnoty pri vyšších frekvenciách: a = d = 256 a b = 0)

3) Odpor (Acos (phi)) a reaktancia (Asin (phi)) sa teraz dajú vypočítať v digitálnych jednotkách

Literatúra: [1] Leonid Matsiev, „Zlepšenie výkonu a univerzálnosti systémov založených na jednofrekvenčných detektoroch DFT, ako sú AD5933“, Electronics 2015, 4, 1-34; doi: 10,3390/elektronika4010001

[2] Konrad Chabowski, Tomasz Piasecki, Andrzej Dzierka, Karol Nitsch, „Jednoduchý merač impedancie širokého frekvenčného rozsahu založený na integrovanom obvode AD5933“, Metrol. Merať Syst., Zv. XXII (2015), č. 1, s. 13-24.

Krok 8: Pokročilé veci: teoretický faktor zisku

Vzhľadom na matematické modelovanie DFT by malo byť tiež možné modelovať celý AFE matematicky. Matematicky môže byť napäťový signál opísaný pomocou sínusovej funkcie s danou pevnou frekvenciou, jednosmerným posunom a striedavou osciláciou so špičkovou amplitúdou. Frekvencia sa počas kroku frekvencie nemení. Pretože faktor zosilnenia mení iba veľkosť impedancie a nie PA, nebudeme sa tu zaoberať žiadnym fázovým posunom indukovaným na signáli.

Tu je krátky súhrn napäťového signálu šíriaceho sa cez AFE:

1) Po fáze predpätia je amplitúda striedavého prúdu stále Upeak = 1,5 V (1 V @ VDD = 3,3 V) a DC offset bol zmenený na VDD/2.

2) V odpore na snímanie prúdu je napätie stále rovnaké ako v predchádzajúcom stupni …

3) … ale vzhľadom na napätie na hojdačke operačného zosilňovača majú striedavé oscilácie veľkosť Z*Upeak/Rcurrent. (DC ofset je zrušený referenčným napätím operačných zosilňovačov VDD/2 - bod otáčania hojdačky - a stáva sa virtuálnym uzemnením v tejto časti obvodu.)

4) Jednotkový zosilňovač pridá DC offset VDD/2 späť a presmeruje signál do vstupného stupňa AD5933.

5) Operačný zosilňovač vo vstupnom štádiu má zosilnenie A = -RFB/Rin a amplitúda striedavého prúdu sa preto stáva (Z*Upeak/Rcurrent)*(RFB/Rin)

6) Tesne pred ADC je programovateľný zosilňovač zisku (PGA) s dvoma nastaveniami zisk 1 alebo 5. Napäťový signál v ADC sa teda stáva: PGA*(Z*Upeak/Rcurrent)*(RFB/Rin)

ADC prevádza signál v (t) na digitálny signál x (t) = u (t) / VDD * 2^7 s 12 -bitovou presnosťou.

Magnitúda A je spojená s impedanciou Z pomocou zosilňovacieho faktora, k, ako A = k * Z, a má približnú hodnotu k = PGA * Upeak * RFB * 2^7 / (VDD * Rcurrent * Rin).

Ak chcete namiesto toho pracovať s faktorom zisku, g = 1 / k a Z = g * A.

Krok 9: Pokročilé veci: posun PA

V [2] zisťujú systematický posun v PA ako funkciu frekvencie. Je to spôsobené časovým oneskorením medzi DAC, kde je generovaný budiaci signál, a DFT, kde je potrebné, aby bol prichádzajúci signál spletený s odchádzajúcim signálom.

Posun je charakterizovaný počtom hodinových cyklov, v ktorých je signál oneskorením medzi DAC a DFT interne v AD5933.

Literatúra: [1] Leonid Matsiev, „Zlepšenie výkonu a univerzálnosti systémov založených na jednofrekvenčných detektoroch DFT, ako sú AD5933“, Electronics 2015, 4, 1-34; doi: 10,3390/elektronika4010001

[2] Konrad Chabowski, Tomasz Piasecki, Andrzej Dzierka, Karol Nitsch, „jednoduchý merač impedancie širokého frekvenčného rozsahu založený na integrovanom obvode AD5933“, Metrol. Merať Syst., Zv. XXII (2015), č. 1, s. 13-24.

Odporúča:

Analýza LTE Cat.M1 PSM (režim úspory energie): 4 kroky

Analýza LTE Cat.M1 PSM (úsporný režim): V predchádzajúcom článku sme diskutovali o tom, ako nastaviť aktívny / spánkový cyklus pomocou PSM. Vysvetlenia nastavenia hardvéru a PSM a príkazu AT nájdete v predchádzajúcom článku. (Odkaz: https://www.instructables.com/id/What-Is-a-PSMPow…Ac

Analýza údajov o teplote/vlhkosti pomocou Ubidotov a tabuliek Google: 6 krokov

Analýza teplôt/vlhkosti pomocou Ubidotov a tabuliek Google: V tomto tutoriáli budeme merať rôzne údaje o teplote a vlhkosti pomocou snímača teploty a vlhkosti. Dozviete sa tiež, ako odoslať tieto údaje do Ubidots. Aby ste ho mohli analyzovať odkiaľkoľvek pre rôzne aplikácie. Tiež odoslaním

Analýza hlavných komponentov: 4 kroky

Principal Component Analysis: Principal Component Analysis je štatistická metóda, ktorá pomocou ortogonálnych transformácií prevádza množinu potenciálne korelovaných premenných na množinu lineárne nekorelovaných hodnôt. Jednoducho povedané, vzhľadom na množinu údajov s viacerými dimenziami to pomáha

Analýza knihy objednávok pomocou farebného senzora: 14 krokov

Analýza knihy objednávok pomocou farebného senzora: Pri červenom/zelenom/modrom farebnom senzore Adafruit TCS34725 na analýzu svetelného výkonu z knihy objednávok na obrazovke pri obchodovaní s kryptom. Ak prevažne „kúpite“prídu objednávky, reprezentované zelenými číslami na obrazovke, možno by ste mohli očakávať

Analýza sentimentu na Twitteri s Raspberry Pi: 3 kroky (s obrázkami)

Analýza sentimentu na Twitteri s Raspberry Pi: Čo je to analýza sentimentu a prečo by vás to malo zaujímať? Analýza sentimentu je proces určovania emocionálneho tónu za sériou slov, ktorý sa používa na porozumenie vyjadreným postojom, názorom a emóciám. v rámci