Obsah:

- Krok 1: Používanie digitálneho sekvencera používateľom

- Krok 2: Technické detaily

- Krok 3: Technické detaily

- Krok 4: 7-segmentový rozdeľovač hodín

- Krok 5: Oddeľovač hodín úderov za minútu

- Krok 6: Delič hodín s rozstupmi

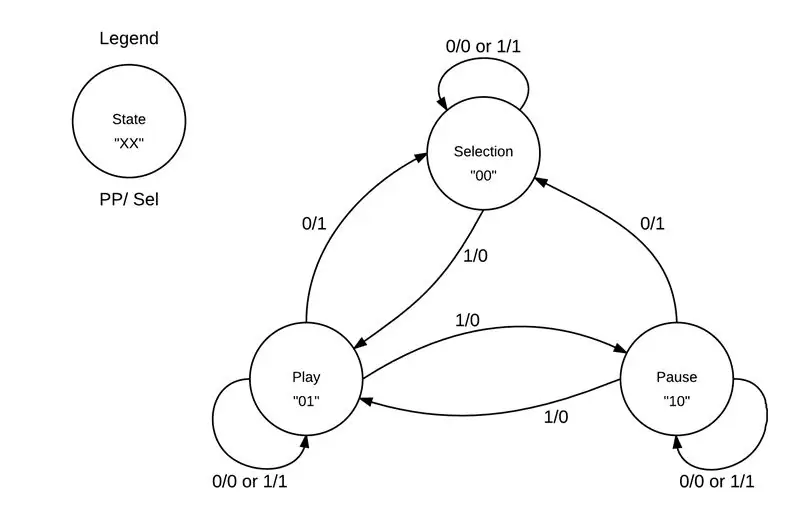

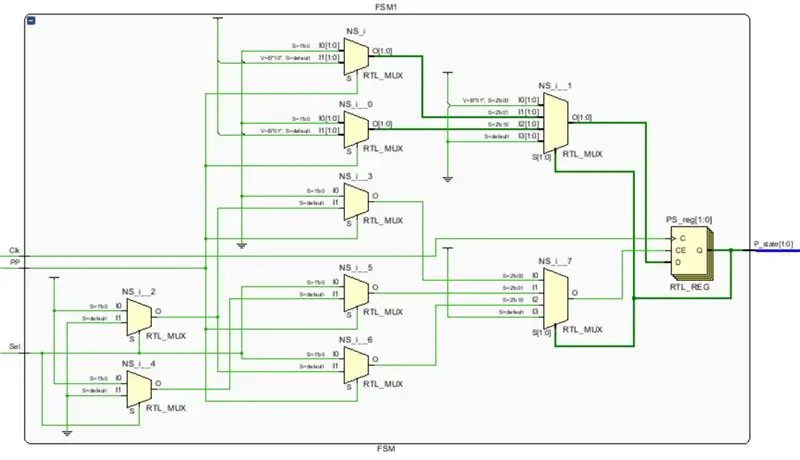

- Krok 7: Play/Pause/Select State Machine

- Krok 8: Play/Pause/Select State Machine

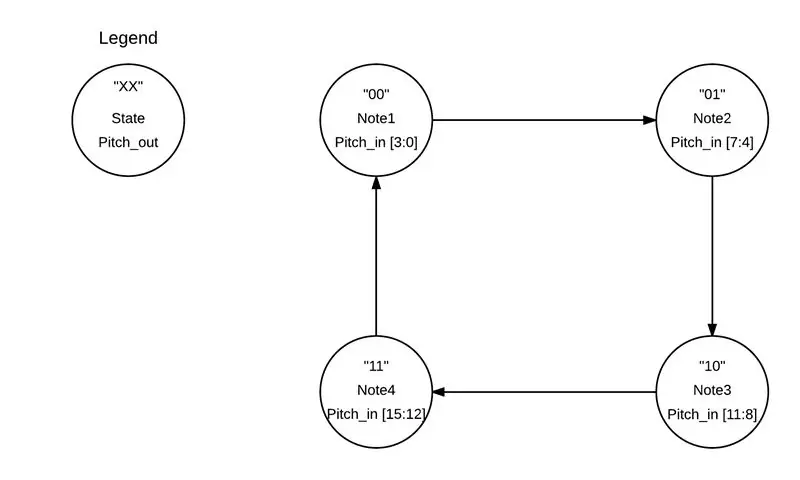

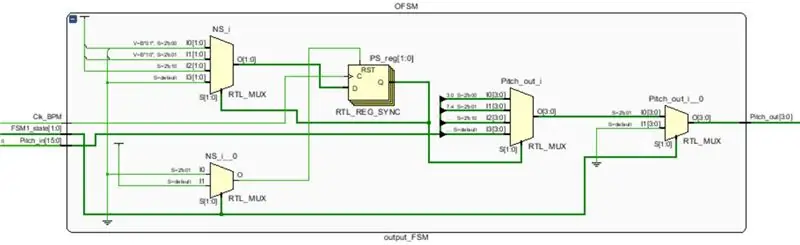

- Krok 9: Výstup FSM

- Krok 10: Výstup FSM

- Krok 11: Priradenie poznámky

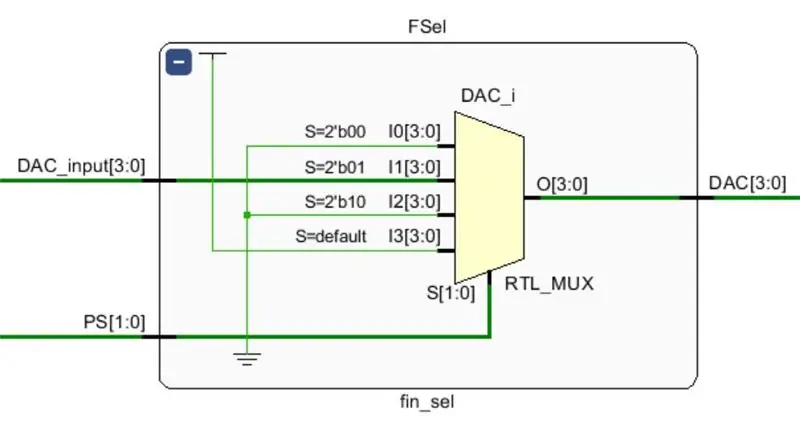

- Krok 12: Výber výstupu

- Krok 13: Square Wave Gen

- Krok 14: 7-segmentový displej

- Krok 15: Konečný výber

- Krok 16: Externé zariadenia: DAC

- Krok 17: Externé zariadenia: reproduktor

- Krok 18: Ukážka videa

- Krok 19: Kód VHDL

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 12:01.

- Naposledy zmenené 2025-01-23 15:06.

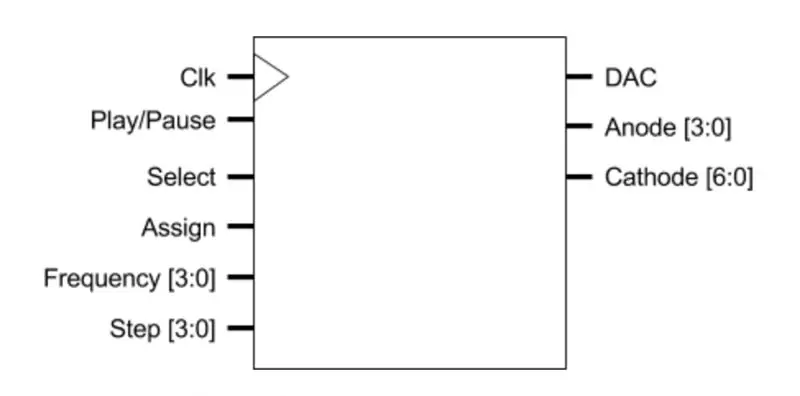

CPE 133, Cal Poly San Luis Obispo

Tvorcovia projektu: Jayson Johnston a Bjorn Nelson

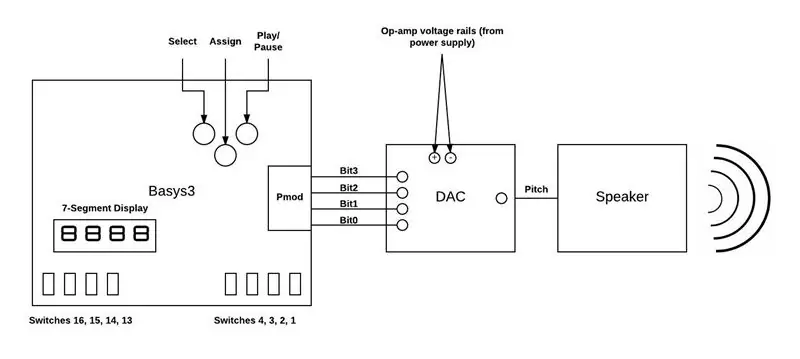

V dnešnom hudobnom priemysle je jedným z najčastejšie používaných „nástrojov“digitálny syntetizátor. Každý žáner hudby, od hip-hopu po pop a dokonca aj krajinu, používa v štúdiu digitálny syntetizátor na vytváranie úderov a zvukov, ktoré sú potrebné na uvedenie ich hudby do života. V tomto návode vytvoríme veľmi jednoduchý syntetizátor s doskou Basys 3 FPGA.

Syntetizátor bude schopný hrať štyri vybrané štvrťtóny pri konštantnom počte úderov za minútu. Používatelia použijú prepínače na priradenie každej noty k hudobnému tónu. Na tento projekt používame 4-bitový prevodník digitálneho signálu na analógový (DAC) na prevzatie výstupu z dosky a jeho konverziu na analógový signál. Výstup z DAC bude potom vedený do štandardného reproduktora počítača, čím vytvoríme našu hudbu. K dispozícii je šestnásť diskrétnych ihrísk. Náš syntetizátor obmedzíme na jednu oktávu s 12 notami, ktoré sa pohybujú medzi stredným C (261,6 Hz) a B4 (493,9 Hz). Užívateľ bude mať tiež možnosť priradiť viac tónov súčasne, ako aj odpočinok tým, že stlačí priradenie, pričom žiadny z výškových spínačov nebude posunutý nahor. Pri výbere a prehrávaní každej noty sa na 7-segmentovom displeji zobrazuje nota s písmenom. Tiež použijeme tri tlačidlá na doske, jedno na prehrávanie a pozastavenie hudby, jedno na vynulovanie syntetizátora a jeho uvedenie do režimu „výberu“a tretie na priradenie výšky tónu v režime výberu.

Hneď ako je používateľ spokojný s výberom tónov a po stlačení tlačidla prehrávania, syntetizátor bude opakovane prehrávať každú notu, kým používateľ nestlačí pauzu alebo nevyberie.

Tu je zoznam požadovaného vybavenia:

- Vivado (alebo akýkoľvek pracovný priestor VHDL)

- Základňa 3 alebo podobná doska FPGA

- Prevodník digitálneho signálu na analógový (min. 4-bitový)

- Reproduktor s konektorom pre slúchadlá

- Drôtené káble

Krok 1: Používanie digitálneho sekvencera používateľom

Nasledujúce kroky slúžia na ovládanie digitálneho sekvencera. Digitálny sekvencer podporuje prehrávanie 12 rôznych výšok (C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B), ktoré sa pohybujú od 261,6 Hz do 493,9 Hz.

1. Stlačením ľavého tlačidla prepnite nástenku do režimu výberu. V tomto režime budú na uloženie odlišnej výšky tónu použité všetky 4 spínače úplne vľavo (prepínače 13 až 16).

2. Ak chcete vykonať výber, zapnite jeden z ľavých prepínačov a potom použite 4 pravé prepínače (prepínače 1 až 4) na výber požadovanej výšky. Rozteč spojená so špecifickou kombináciou pravých spínačov sa zobrazí na sedemsegmentovom displeji a displej sa aktualizuje na novú priradenú výšku vždy, keď sa pravé prepínače posunú na novú kombináciu. Odpočinok je možné priradiť tak, že nikdy nezaradíte výšku tónu jednému z ľavých spínačov, alebo priradením výšky tónu, ktorý je na displeji zobrazený ako 0. Hneď ako sa nájde požadovaná výška a zobrazí sa na displeji, stlačením spodného tlačidla priradenia priradíte konkrétnej tóne notu.

3. Zopakujte krok 2 pre tri zostávajúce tóny tak, že každý zo zostávajúcich ľavých prepínačov zapnete jednotlivo, pravými prepínačmi vyberiete príslušnú výšku tónu a stlačením spodného tlačidla tónu priradíte tón. Viacnásobným notám je možné priradiť rovnakú výšku posunutím viac ako jedného ľavého spínača nahor.

4. Teraz, keď sú priradené všetky výšky tónov, je digitálny sekvencer pripravený hrať. Ak chcete prehrať poznámky na reproduktore, jednoducho stlačte pravé tlačidlo prehrávania/pozastavenia a spustite prehrávanie hudby. Poradie sekvencie prehrávania odzrkadľuje výšky tónov priradené ľavým prepínačom zľava doprava. Noty sa budú hrať stanoveným počtom úderov za minútu v poradí 1, 2, 3, 4, 1, 2…. Počas reprodukcie hudby na displeji sa na displeji zobrazí poznámka, ktorá sa práve prehráva. Ak chcete prehrávanie hudby pozastaviť, stačí stlačiť pravé tlačidlo. Potom sa hudba zastaví a na displeji sa zobrazí symbol pauzy. Ďalším stlačením pravého tlačidla sa obnoví prehrávanie.

Krok 2: Technické detaily

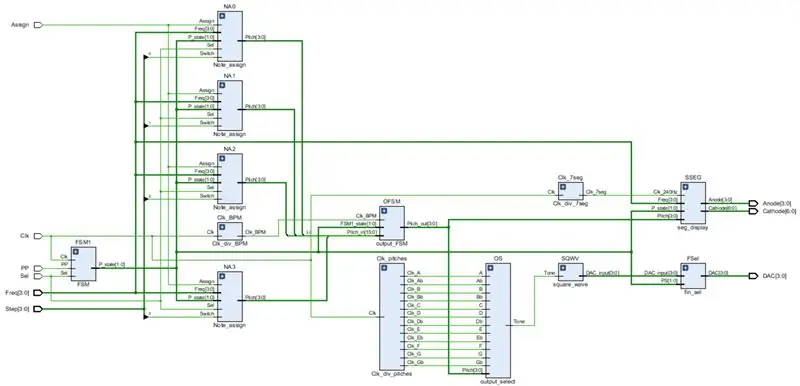

Náš syntetizátor využíva mnoho rôznych digitálnych komponentov. Zahrnuté sú stroje s konečným stavom, registre, multiplexory, rozdeľovače hodín a ďalšie. Na zostavenie nášho syntetizátora sme použili 10 unikátnych modulárnych súborov. Namiesto toho, aby sme z každého modulu urobili súčasť, sme modulárne súbory rozdelili podľa funkcií. Väčšina modulov je v dôsledku toho viac ako jednou súčasťou. Všimnite si obrázok na obrázku vyššie, ktorý zobrazuje každý blok zviazaný v našom najvyššom prevedení.

Každý modul prediskutujeme popisom vstupov a výstupov, rozdelením jeho komponentov a vysvetlením jeho účelu v celkovom dizajne. V spodnej časti návodu sa nachádza súbor ZIP, ktorý obsahuje každý súbor kódu VHDL použitý v projekte.

Vstupy

- Clk (natívny hodinový signál)

- PP (prehrávanie/pauza)

- Sel (prepnite syntetizátor do režimu výberu)

- Priradiť (priradiť kroku výšku tónu)

- Krok (pozičné poznámky)

- Freq (prepínače vytvárajúce požadovanú výšku)

Výstupy

- Anóda (7-segmentové anódy)

- Katóda (7-segmentové katódy)

- DAC (4-bitové riadenie DAC)

Krok 3: Technické detaily

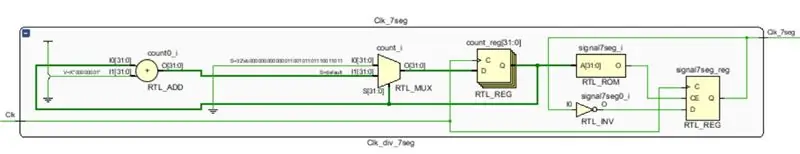

Krok 4: 7-segmentový rozdeľovač hodín

Náš syntetizátor používa tri rozdeľovače hodín, všetky produkujúce signály, ktoré v našom projekte slúžia inému účelu. Oddeľovač hodín prijíma pôvodný hodinový signál a vytvára zmenený signál, ktorý má frekvenciu nižšiu ako pôvodný hodinový signál. Natívny takt Basys 3 je 100 MHz. Toto je frekvencia, ktorú používajú naše rozdeľovače hodín. Ak používate inú dosku FPGA s inou natívnou frekvenciou hodín, možno budete musieť kód zmeniť.

7-segmentový delič hodín vytvára signál, ktorý poháňa súbor seg_display. Ako tento súbor funguje, podrobnejšie vysvetlíme, keď sa dostaneme do jeho sekcie. Tento delič hodín v zásade vytvára signál 240 Hz, ktorý sa použije na prepínanie medzi anódami a katódami na displeji. Signál je 240 Hz, pretože frekvencia, pri ktorej ľudské oko nemôže rozpoznať neprítomnosť svetla, je 60 Hz. Používame dve číslice, takže zdvojnásobením tejto frekvencie bude každá číslica oscilovať pri 60 Hz. Potom ho zdvojnásobíme, aby sme dostali 240 Hz, pretože systém sa mení iba vtedy, keď je signál vysoký, nie keď klesá.

Aby to bolo dosiahnuté, delič vezme pôvodný signál 100 MHz a počíta s každou rastúcou hranou. Keď počítadlo dosiahne 416667, výstup prejde z nízkeho na vysoký alebo naopak.

Vstupy

Clk (natívny hodinový signál)

Výstupy

Clk_7seg (na zobrazenie seg_display)

Komponenty

- D register

- MUX

- Invertor

- Sčítač

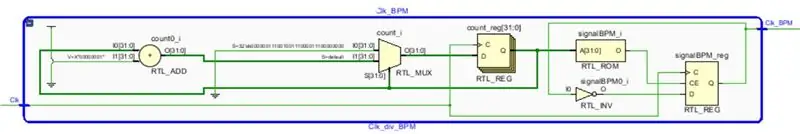

Krok 5: Oddeľovač hodín úderov za minútu

Oddeľovač hodín BPM funguje podobným spôsobom. Tento delič vytvára hodinovú frekvenciu, ktorá riadi prepínanie medzi štyrmi krokmi pri výstupe tónov v stave prehrávania. Rozhodli sme sa prepínať medzi notami pri 100 BPM. Pri 100 úderoch za minútu sa každá nota bude hrať 3/5 sekundy. Výsledný signál by mal frekvenciu 1,67 Hz.

Na vytvorenie signálu tejto frekvencie sme opäť použili počítací systém, ale tentoraz bol počet 60 miliónov. Zakaždým, keď počítadlo dosiahne 60 miliónov, výstupný signál sa bude prepínať vysoko alebo nízko.

Vstupy

Clk (natívna hodinová frekvencia)

Výstupy

Clk_BPM (to output_FSM)

Komponenty

- D register

- MUX

- Invertor

- Sčítač

Krok 6: Delič hodín s rozstupmi

Rozdeľovač hodín Pitches je najväčší z našich rozdeľovačov hodín. Tento delič vydáva 12 rôznych signálov zodpovedajúcich 12 rôznym notám, ktoré môže náš syntetizátor hrať. Na základe základných znalostí z hudobnej teórie sme usúdili, že bit alebo zbernica môžu oscilovať rýchlosťou, ktorá zodpovedá frekvencii hudobných tónov. Tu nájdete frekvencie, ktoré sme použili. Použili sme štvrtú oktávu výšok.

Tu sa používa rovnaký systém počítania. Konkrétne hodnoty, do ktorých sme počítali, nájdete v súbore označenom Clk_div_pitches.

Vstupy

Clk (natívna hodinová frekvencia)

Výstupy

C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (na výber_výstupu)

Komponenty

- D register

- MUX

- Invertor

- Sčítač

Krok 7: Play/Pause/Select State Machine

V našom projekte sú dva stroje s konečným stavom (FSM). FSM je logické zariadenie, ktoré môže existovať iba v jednom stave z konečného počtu stavov. Pomocou FSM sa digitálny obvod môže presunúť do nového stavu na základe kombinácie vstupov. Použitím vstupnej logiky sa stav FSM zmení, keď bude stúpajúca hrana hodín. Zo stavu a vstupov do obvodu môžete vytvoriť logiku výstupu, ktorá dáva výstupy, ktoré existujú iba vtedy, ak je FSM v určitom stave.

Stavový stroj PPS je prvým FSM v našom obvode. V tomto FSM sú tri štáty; Režim prehrávania, pozastavenia a výberu. Na pohyb v rôznych stavoch sme použili tlačidlá PP a Výber. Pozrite sa na stavový diagram vyššie a zistite, ako dochádza k prechodom medzi stavmi. Tento prechod FSM sme urobili na stúpajúcej hrane natívnych 100 MHz taktov, aby bolo nemožné, aby sa stroj neprechodil po stlačení jedného z tlačidiel, a to ani na veľmi krátky čas. Súčasný stav (P_state) je jediným výstupom z tohto modulu.

Vstupy

- Clk (natívna hodinová frekvencia)

- Sel (ľavé tlačidlo)

- PP (pravé tlačidlo)

Výstupy

P_state (súčasný stav, na výstup_FSM, poznámka_ priradenie, seg_dsiplay, konečný_výber)

Komponenty

- MUX

- D register

Krok 8: Play/Pause/Select State Machine

Krok 9: Výstup FSM

Toto je druhý FSM, na ktorý sa odkazuje v predchádzajúcej časti. Tento FSM plní inú funkciu ako ostatné, ale základ pre tento je v zásade rovnaký.

Výstupný FSM funguje iba vtedy, ak je súčasný stav z prvého FSM „01“(stav prehrávania). V zásade ide o povolenie modulu. Ak je stav „01“, FSM sa bude prepínať medzi stavmi na stúpajúcej hrane hodinového signálu BPM. Robíme to, pretože output_FSM riadi, ktoré binárne číslo pre zvolené ihrisko bude odoslané do modulov output_select a seg_display. FSM má 16-bitový vstup pochádzajúci z modulu na priradenie noty, ktorý bude popísaný ďalej. V stave „00“pre output_FSM modul vydá „xxxx“pre prvú priradenú notu. Potom v „01“vydá „yyyy“pre druhú notu a podobne pre každú notu, potom sa vráti k prvej note. Pozri stavový diagram vyššie.

Tento FSM sa líši od prvého, pretože neexistuje žiadna vstupná logika na ovládanie prepínania medzi stavmi. Namiesto toho bude FSM fungovať iba vtedy, keď je stav z prvého FSM „01“, a potom tento FSM bude prechádzať medzi stavmi iba na stúpajúcej hrane hodinového signálu. Ďalším rozdielom je, že tento modul má výstupnú logiku, čo znamená, že nevydáva súčasný stav, ale vydáva binárne číslo pre výšku v tomto stave.

Vstupy

- Clk_BPM (hodinový signál BPM z deliča hodín)

- FSM1_state (PS z PPS FSM)

- Pitch_in (rozstupy od note_assign)

Výstupy

Pitch_out (vždy po jednom tóne, na output_select a seg_display)

Komponenty

- MUX

- D register

Krok 10: Výstup FSM

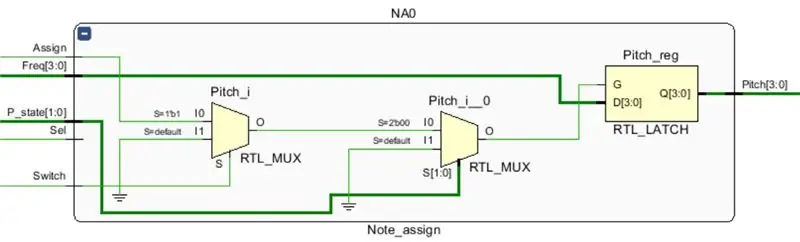

Krok 11: Priradenie poznámky

Modul priradenia noty je zodpovedný za skutočne priradenie výšky pozičnej note alebo kroku. Tento modul je v skutočnosti veľmi jednoduchý. Najprv skontroluje, či je obvod v stave "výberu" a či je krokový spínač (úplne vľavo) vysoko. Ak je to pravda a stlačíte tlačidlo priradenia, výstup modulu sa bude rovnať binárnemu číslu reprezentovanému frekvenčnými spínačmi (úplne vpravo).

Pôvodne sme sa pokúsili vytvoriť modul, ktorý by v skutočnosti uložil jeden zo signálov hodinových tónov na výstup, ale vyskytli sa problémy s tým, že výstup sa zmenil tak, aby sledoval vstupné hodinové signály. Toto je jediný modul, ktorý sa vo finálnom návrhu použil viac ako raz. Ku každému kroku je priradený modul note_ assign, a preto každá inštancia modulu dostane jeden bit zbernice Step.

Vstupy

- P_state (súčasný stav z PPS FSM)

- Sel (ľavé tlačidlo)

- Prepínač (jednokrokový prepínač)

- Freq (krajné pravé prepínače pre výšku tónu)

- Priradiť (spodné tlačidlo, priradí poznámku)

Výstupy

Rozteč (binárne číslo, na výstup_FSM)

Komponenty

- MUX

- D registrovať

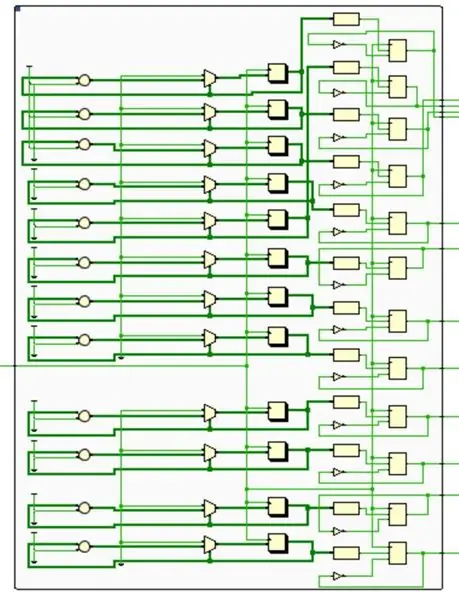

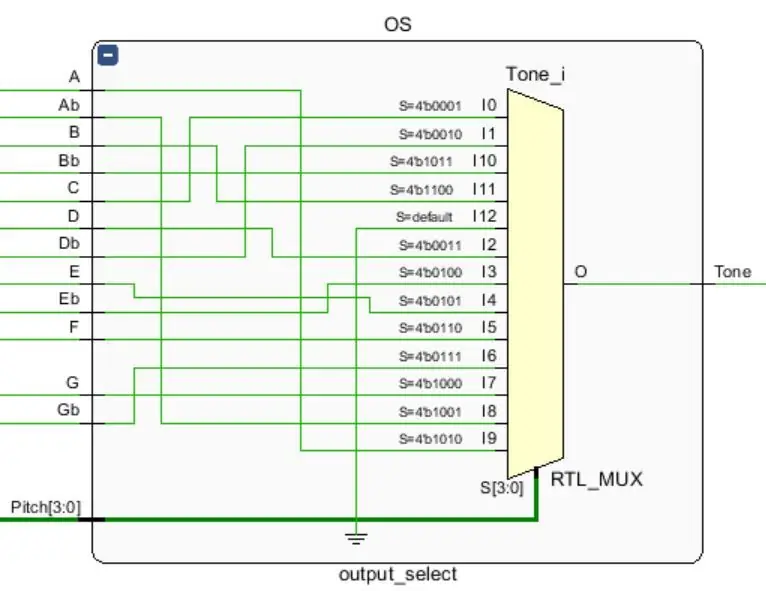

Krok 12: Výber výstupu

Výber výstupu je zodpovedný za prevzatie binárneho čísla pre výšku tónu a jeho pripojenie k príslušnému hodinovému signálu. Napriek svojej veľkosti sa jedná o relatívne jednoduchý modul. Output_select je v podstate binárny dekodér, ktorý dekóduje binárne číslo pre výšku tónu na konkrétny hodinový signál. Vlastné priradenie výstupu k hodinovej frekvencii tu fungovalo lepšie v porovnaní s modulom note_ assign, pretože tento modul musel iba MUXOVAŤ hodinové signály s binárnym číslom predstavujúcim riadiaci vstup.

Ospravedlňujeme sa za podivné smerovanie, Vivado usporiadal signály tónu abecedne pre súbor clk_div_pitches, ale pre tento súbor ich usporiadal vzostupne podľa binárneho čísla, čo spôsobilo, že výšky tónov sú v inom poradí. Všimnite si tiež, že ak bolo binárne číslo z output_FSM „0000“alebo čokoľvek väčšie ako „1100“, potom MUX odoslal plochý signál „0“.

Vstup

- Rozteč (z output_FSM);

- C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (signály hodín tónu)

Výkon

Tón (jeden bit, ktorý zodpovedá zvolenému hodinovému signálu, na square_wave)

Komponenty

MUX

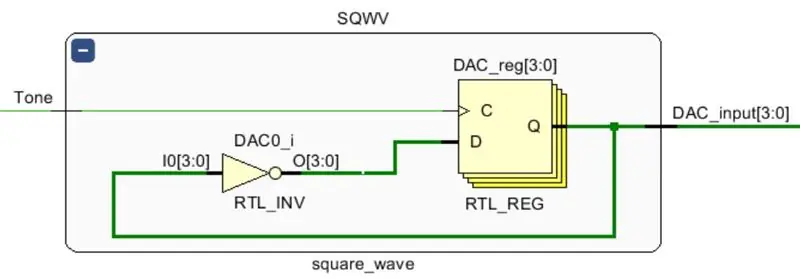

Krok 13: Square Wave Gen

Modul square_wave je generátor štvorcovej vlny, ktorá je na výstupe z dosky do DAC. S použitím tónového signálu z predchádzajúceho súboru táto square_wave invertuje 4 -bitové číslo medzi „0000“a „1111“na stúpajúcej hrane Tónu. Tón je špecifická frekvencia tónu, takže square_wave vytvára vlnu s inou frekvenciou, keď output_FSM prechádza do iného stavu. 4-bitový výstup z tohto modulu smeruje do modulu fin_sel, kde logika určuje, či bude táto zbernica vyvedená na základe stavu z PPS FSM.

Alternatívou k tomuto generátoru štvorcových vĺn je výroba sínusovej vlny. Aj keď by to s najväčšou pravdepodobnosťou poskytlo lepší konečný tón, implementácia je podstatne ťažšia, preto sme sa rozhodli generovať iba štvorcovú vlnu.

Vstupy

Tón (oscilačný bit z output_select)

Výstupy

DAC_input (oscilačná 4-bitová zbernica, ktorá sa mení s rovnakou frekvenciou tónu)

Komponenty

- Invertor

- D register

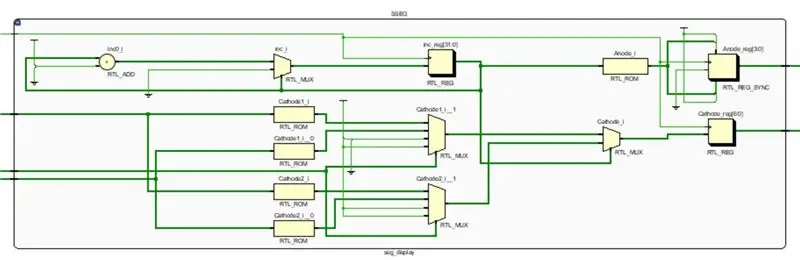

Krok 14: 7-segmentový displej

Modul seg_display ovláda 7-segmentový displej na našej základnej doske. V rámci modulu prebiehajú dva procesy. Prvý proces dekóduje Freq v stave „výberu“alebo Pitch v režime „prehrávania“. V režime „pauza“modul dekóduje, aby zobrazil symbol pauzy. Pri pohľade na kód VHDL vidíte, že binárny dekodér v skutočnosti dekóduje vstup na dva rôzne signály, katódu 1 a katódu 2. Katóda 1 predstavuje písmeno zodpovedajúce výške, ktorá sa má zobraziť, a katóda 2 predstavuje plochý symbol (b), ak existuje. Dôvodom je druhý proces vykonaný modulom seg_display.

Na doske basys3 má segmentový displej spoločné katódy. Kým anódy riadia, ktorá číslica je zapnutá, katódy riadia, ktoré segmenty sú zapnuté. Keďže displej má bežné katódy, znamená to, že naraz môžete zobraziť iba jednu sadu segmentov. To predstavuje problém pre tento projekt, pretože chceme v prípade potreby súčasne zobraziť písmeno na prvej číslici a plochý symbol. Teraz si spomeniete na hodinový signál 7seg? Aby sme tento problém vyriešili, meníme anódy a katódy tam a späť na hodinovom signáli 7seg. Pretože hodinový signál je 240 Hz a používame dve číslice, každá číslica bude oscilovať pri 60 Hz. Pre ľudské oko to bude vyzerať, že číslice vôbec nekmitajú.

Všimnite si tiež, že displej dosky basys3 používa negatívnu logiku. To znamená, že ak je anóda alebo katóda nastavená na „0“, táto číslica alebo segment budú zapnuté a naopak.

Vstupy

- Rozteč (binárne číslo pre notu, používané v stave hry)

- Freq (frekvenčné spínače, používané v stave výberu)

- P_state (súčasný stav z PPS FSM)

- Clk_240Hz (hodinový signál z Clk_div_7seg, dvojnásobok 120, pretože používame iba stúpajúcu hranu)

Výstupy

- Katóda (zbernica, ktorá ovláda segmenty na displeji, konečný výstup)

- Anóda (zbernica, ktorá riadi číslice na displeji, konečný výstup)

Komponenty

- Západka

- MUX

- D register

Krok 15: Konečný výber

Final select je posledný modul použitý v tomto projekte. Ďalší jednoduchý modul, tento modul riadi konečný výstup, ktorý bude smerovať do DAC. Keď je modul v stave „výber“alebo „pozastavenie“, vydá statický signál „0000“, takže z reproduktorov sa nebude prehrávať žiadna hudba. V stave „hrať“modul bude vydávať oscilačné 4-bity určené square_wave.

Vstupy

- P_state (súčasný stav z PPS FSM)

- DAC_input (oscilačné 4-bity z square_wave)

Výstupy

DAC (rovná sa DAC_vstup v stave prehrávania, konečný výstup)

Komponenty

MUX

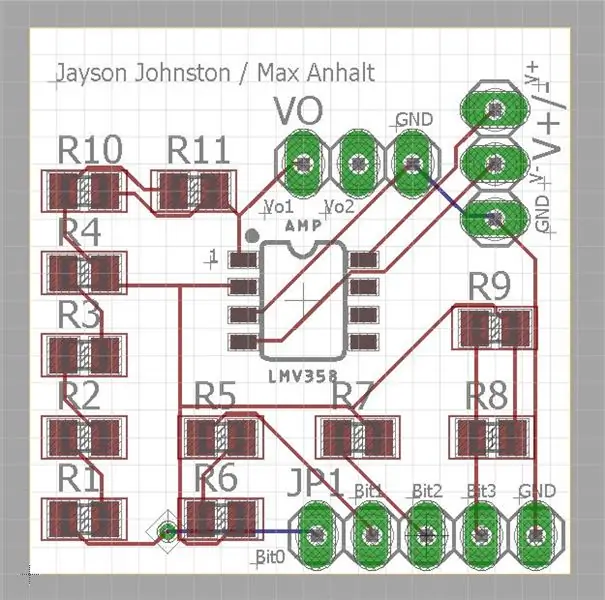

Krok 16: Externé zariadenia: DAC

Prevodník digitálneho signálu na analógový (DAC) zachytáva diskrétny signál a prevádza ho na súvislý signál. Náš DAC má štyri bity a je vyrobený zo súčtového zosilňovača. Použitím pomeru odporov v napájacej a spätnoväzbovej slučke sa nám podarilo vytvoriť systém, ktorý výstupmi na 16 rôznych úrovniach vytvára „súčtom“každej vetvy. Bit0, horná vetva, má najmenšiu hmotnosť a keď je vysoká, prispieva k najmenšiemu potenciálu, pretože má vyšší odpor. Hmotnosť sa zvyšuje, keď idete po vetvách. Ak by ste mali počítať binárne hore a potom dole pomocou bitových vstupov, výstupné napätie by vyzeralo ako stupňovitá sínusová vlna. Vstup na DAC bol pripojený k jednému z PMOD na doske na prenos 4-bitového signálu.

DAC bol pôvodne zostavený pre triedu elektrotechniky a bol navrhnutý a spájkovaný nami, nie je kúpený v obchode. Hore je obrázok súboru s návrhom na vytvorenie dosky plošných spojov.

Krok 17: Externé zariadenia: reproduktor

Pre tento projekt nebudete chcieť kúpiť super pekný pár reproduktorov. Ako môžete povedať, zvuk je celkom základný. Išli sme a kúpili sme si sadu reproduktorov k počítaču za 8 dolárov od Best Buy. Všetko, čo má konektor pre slúchadlá, funguje dobre. Monotónny tiež funguje dobre. Môžete dokonca použiť slúchadlá, ale môžete ich sfúknuť!

Na pripojenie výstupu DAC k reproduktorom sme použili prepojovacie káble a potom sme držali výstupný kábel za špičku konektora pre slúchadlá a kábel pre uzemnenie k základni. Pokúsili sme sa použiť elektrickú pásku na držanie káblov na mieste, ale spôsobovalo to veľa rušenia. Tento problém by mohlo vyriešiť vyskúšanie iného štýlu pásky.

U našich reproduktorov sme ich prepli na najvyššie nastavenie a dostali sme slušne hlasný hluk.

A to je posledný krok k vytvoreniu digitálneho sekvencera z dosky FPGA! Prejdite do ďalších dvoch sekcií, stiahnite si celý náš kód VHDL a pozrite sa na sekvencer v prevádzke.

Krok 18: Ukážka videa

Toto video ukazuje konečnú verziu pracovného projektu vrátane postupu priradenia prepínačov k 4 rôznym výškam a reproduktorov, ktoré hrajú príslušné tóny.

Krok 19: Kód VHDL

Tu je kód celého projektu vrátane obmedzení a súborov sim použitých pri vytváraní sekvencera. Všimnite si toho, že v architektúre to hovoria nepoužité súbory návrhu.

Odporúča:

Výkonný digitálny stmievač striedavého prúdu s použitím STM32: 15 krokov (s obrázkami)

Výkonný digitálny stmievač striedavého prúdu pomocou STM32: Hesam Moshiri, hesam.moshiri@gmail.com AC záťaže žijú s nami! Pretože sú všade okolo nás a prinajmenšom domáce spotrebiče sú napájané zo siete. Mnoho typov priemyselných zariadení je napájaných aj z jednofázového 220V-AC.

Sekvencer sekcie rytmu MIDI Arduino: 8 krokov (s obrázkami)

Sekvencer MIDI rytmickej sekcie Arduino: Mať dobrý softvérový bicie stroj je dnes jednoduché a lacné, ale používanie myši mi zabíja zábavu. Preto som si uvedomil, čo bolo pôvodne zamýšľané ako čistý 64 -stupňový hardvérový MIDI bubnový sekvencer schopný spustiť až 12 rôznych bicích elem

Jednoduchý sekvencer: 16 krokov (s obrázkami)

Simple Sequencer: Jedným z kľúčov k dobrej hudbe je bezduché opakovanie. V tom je jednoduchý sekvencer skvelý. Robí to isté znova a znova v sekvencii ôsmich nôt. Môžete nastaviť frekvenciu poznámky, trvanie poznámky a

(takmer) Univerzálny MIDI SysEx CC programátor (a sekvencer ): 7 krokov (s obrázkami)

(Takmer) univerzálny MIDI SysEx CC programátor (a sekvencer …): V polovici osemdesiatych rokov začali výrobcovia syntetizátorov „menej je lepšie“; proces, ktorý viedol k syntetizátorom barebones. To umožnilo zníženie nákladov na strane výrobcu, ale spôsobilo, že proces opravy je pre konečné použitie nudný, ak nie nemožný

Programovateľný RGB LED sekvencer (pomocou Arduino a Adafruit Trellis): 7 krokov (s obrázkami)

Programovateľný RGB LED sekvencer (s použitím Arduino a Adafruit Trellis): Moji synovia chceli, aby ich pásy rozžiarili farebné LED pásy, a ja som nechcel používať konzervovaný RGB pásový ovládač, pretože som vedel, že sa s pevnými vzormi nudia. tieto ovládače majú. Tiež som si myslel, že by to bola skvelá príležitosť na vytvorenie