Obsah:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:55.

- Naposledy zmenené 2025-01-23 15:05.

JDM je populárny programátor PIC, pretože používa sériový port, minimum komponentov a nevyžaduje žiadne napájanie. Existuje však zmätok, s mnohými variáciami programátora na internete, ktoré pracujú s ktorými obrázkami? V tomto „pokyne“testujeme JDM a demonštrujem, ako simulovať obvod pomocou Spice, ktorý zodpovie všetky vaše otázky!

Zásoby

LTspice, ktorý je možné stiahnuť z analógových zariadení tu.

Tu tiež potrebujete súbory obvodu JDM.

Krok 1: Požiadavky na sériový port

JDM vyžaduje sériový port zodpovedajúci špecifikácii EIA232, ideálne s úrovňami napätia +12/-12.

Podľa technického listu Texas Instruments Line Driver MC1488 (obrázok 3)

Výstupná impedancia = 4V/8mA = 500 ohmov.

Limit skratového prúdu = 12 mV, bez časového obmedzenia - bez poškodenia čipu.

Vstupná impedancia linkového prijímača = odporúča sa 3k až 7k ohm.

Sériové porty na starších stolných počítačoch používajú +12 V/-12 V, ktoré spĺňajú túto požiadavku.

Sériové porty na novších prenosných počítačoch používajú nižšie napätie. JDM môže, ale nemusí fungovať - odpoveď je zložitejšia.

Krok 2: Požiadavky na programovanie PIC

Informácie o programovacích požiadavkách PIC sú získané od spoločnosti Microchip. Vyššie uvedené platí pre typické zariadenie.

Krok 3: Špecifikácia JDM

Stratila sa pôvodná webová stránka JDM v hmlách času? Necháme sa hádať, čo pôvodne dizajnér pre špecifikáciu zamýšľal.

- Poskytujte VDD = 5V a maximálne IDD = 2mA (pre verziu „v zásuvke“)

- Zabezpečte VHH = 13 V a maximálne IHH = 0,2 mA.

- MCLR Čas nábehu tVHHR = 1uS max.

- Verzia ICSP musí byť schopná vytiahnuť MCLR nízko proti 22 k prítlaku na cieľ.

Krok 4: Popis obvodu

Obrázok JDM1 je založený na „štandardnom“obvode JDM prevzatom z webovej stránky PICPgm. Toto je programátor „PIC in Socket“, kde PIC preberá energiu z pinov TX a RTS. Pôvodný diagram bol ťažko zrozumiteľný, takže som ho prekreslil pomocou normálnej konvencie toku prúdu zhora nadol. A pridal som LED indikátory „RESET“, „PROG“a „RTS“, ktoré sú potrebné pri konštrukcii a testovaní. Našťastie tieto nemajú žiadny škodlivý vplyv na správanie.

Normálna konvencia návrhu obvodu je spoločná pre všetky dôvody, ale kľúčovou vlastnosťou JDM je, že uzemnenie sériového portu (GND) je pripojené k VDD. To spôsobuje zmätok, pretože signály sériového portu sa merajú vzhľadom na GND, signály PIC vzhľadom na logickú zem (VSS).

Keď sa TX zvýši, Q1 sa správa ako dve predpäté diódy vpred. (Kolektor Q1 nie je reverzne predpätý ako pri normálnej prevádzke s tranzistorom). Kolektor Q1 nabíja C2, ktorý je Zenerom (D3) upnutý na VDD+8V. Vysielač Q1 dodáva do MCLR 13V pre režim Program/Verify.

Keď sa TX zníži, kondenzátor C3 sa nabije cez D1 a VSS sa zenerom (D5) upne na VDD-5V. Tiež TX je upnutý na (VSS-0,6) pomocou D1. Q1 je vypnutý, C1 si drží náboj pre ďalší programovací impulz. MCLR je upnutý na 0 V pomocou D2, takže PIC je teraz Reset.

Keď je RTS vysoký, hodiny sa prenášajú do PGC. Svorka D4 PGC pri logike VDD vysoká. Keď je RTS nízka, kondenzátor C3 sa nabíja cez D6 a VSS sa upína na VDD-5V zenerom (D5). D6 upína PGC na VSS alebo logickú 0.

Počas programovania sa dáta odoslané na DTR načítajú na PGD, ktoré PIC konfiguruje ako vstup. Keď je DTR vysoké, Q2 funguje ako „sledovateľ emitorov“a napätie PGD je asi (VDD-0,6) alebo logické 1. Keď je DTR nízke, Q2 funguje ako zlý tranzistor (piny emitora a kolektora sú obrátené). Q2 ťahá PGD low, ktoré je upnuté D7 na VSS alebo logike 0.

Počas overovania PIC konfiguruje PGD ako výstup na odosielanie údajov na sériový port. DTR musí byť nastavené vysoko a údaje sa čítajú na CTS. Keď je výstup PGD vysoký, Q2 je vypnutý, CTS = DTR = +12V. Keď je výstup PGD nízky, Q2 je zapnutý. Kolektor Q2 odoberá prúd (12V+5V)/(1k+1k5) = 7mA z DTR a ťahá CTS nízko do VSS.

Krok 5: Príprava na simuláciu

Stiahnite si korenie LT, uložte a otvorte tu uvedené súbory obvodov (*.asc). Na simuláciu obvodu mu musíme dať niekoľko vstupov, potom „vystopovať“výstupy. V1, V2 V3 simulujú sériový port 12V s výstupnou impedanciou R11, R12, R13.

- V1 generuje 2 programové impulzy na TX od 0,5 ms do 4,5 ms

- V2 generuje sériu dátových impulzov na DTR od 1,5 do 4,5 ms

- V3 generuje sériu hodinových impulzov na RTS od 0,5 do 3,5 ms

Komponenty V4, X1, R15 a R16 sú súčasťou simulácie.

- V4 generuje 2 impulzy od 2,5 do 4,5 ms na overenie údajov.

- Jumper X1 simuluje VÝSTUP na PGD.

- R15, R16 simulujú „načítanie“PIC na VDD a MCLR.

Krok 6: Úpravy pre ICSP

Obrázok JDM3 zobrazuje verziu pre programovanie „v obvode“. Úpravy oproti originálu sú

- Vymeňte zásuvku ZIF za konektor ICSP.

- PIC je teraz napájaný napájaním cieľového obvodu (V5).

- Odstráňte 5V zener (D5).

- Malý kondenzátor 100 pF (C4) je presunutý vedľa PIC v cieľovom obvode.

- LED diódy odoberajú energiu z dosky plošných spojov, kde je to možné.

- Na cieľovom obvode je potrebný pull-up odpor MCLR (R10) a dióda (D10).

- POZOR. Cieľová doska musí mať „plávajúci“zdroj, ideálne batériu.

- Nepripájajte cieľovú zem (VSS) k uzemneniu počítača/počítača tak, že súčasne s JDM pripojíte akékoľvek iné počítačové porty.

Po simulácii JDM1 sa ukázal problém dlhého času nabíjania na C2. Potom, čo som si prečítal Fruttenboel, sa zdá, že C2 a Q1 boli pridané ako modifikácia k originálu. Nedokážem si predstaviť, čo majú C2 a Q1 robiť, okrem vytvárania problémov. Takže pre JDM4 sa vrátime k staršiemu dizajnu na Fruttenboel, ktorý je jednoduchý a zrozumiteľný. D1 a D3/LED2 svorka MCLR medzi VSS a VDD+8V. Hodnota R1 sa zníži na 3k3, čo je dostatočné na osvetlenie LED2 pri 12 V.

JDM4 je tiež navrhnutý tak, aby pracoval so slabšími sériovými portami. Keď sa TX zvýši (+9V), zdroj prúdu TX = (9-8)/(1k +3k3) = 0,2 ma, dosť na to, aby vytiahol MCLR vysoko, aj keď nedostatočne na osvetlenie LED2. Keď TX klesne (asi -7V), prúdový odber TX = (9-7)/1k = 2mA. LED1 prúd = (7-2 pre LED)/(2k7) = 1,8 mA. Spúšťací prúd MCLR = 7-5,5/3k3 = 0,5mA.

Tento obvod bol tiež testovaný (simulácia JDM5), aby sa zistilo, čo sa deje so sériovými portami minimálne +/- 7V, kde nie je dostatočné napätie na udržanie VHH = 13V. Účel C1 je teraz zrejmý. C1 vytvára krátke +ve zosilnenie pre MCLR, 33 -bodový hrot na stúpajúcej hrane TX, dostatočne dlhý na to, aby PIC mohol vstúpiť do režimu programovania, možno? Odstráňte však prepojku X2 (deaktivujte LED1), pretože nie je dostatok prúdu na to, aby sa MCLR znížilo a rozsvietilo sa LED1 dohromady. Keď sa TX zníži, prúdový odber TX = (7V-5,5V)/(1k+3k3) = 0,3mA, stačí na to, aby bol MCLR nízko vytiahnutý proti výsuvu R10.

Krok 7: Výsledky simulácie

Ak chcete zobraziť grafické súbory, je lepšie kliknúť pravým tlačidlom myši na nižšie uvedené odkazy a potom vybrať „Otvoriť odkaz na novej karte“

Simulácia 1: stopa MCLR, VSS a RTS pre pôvodný JDM1. Okamžite je zrejmé pozorovanie 1, 2 a 3.

Simulation 2: trace of MCLR and VSS, and RTS for modified JDM2, which fixes previous problems.

Simulácia 3: sledovanie PGD, VSS a PGC pre odosielanie údajov JDM2 v režime programu. Pozorovanie 4 pri 3,5 mS.

Simulácia 4: stopa PGD, VSS a CTS pre JDM2 v overovacom režime (vložený prepojka X1). OK

Simulácia 5: stopa MCLR, VSS, PGD a PGC pre JDM3. ICSP využívajúci energiu z obvodu rieši mnoho problémov.

Simulácia 6: Stopa MCLR, VSS, PGD a PGC pre JDM4 so +/- 9V sériovým portom. MCLR okamžite stúpa, je plne funkčný.

Simulácia 7: Stopa MCLR, VSS a TX pre JDM5 so odstráneným sériovým portom +/- 7V a prepojkou X2. C1 vytvára kladný nárast (špička) na stúpajúcej hrane MCLR, takmer postačujúci na posunutie MCLR nad TX na 13V.

Krok 8: Závery

Spice je skutočne dobrý v odhaľovaní „skrytých tajomstiev“prevádzky na okruhu. Okruh JDM evidentne funguje a je kompatibilný s mnohými čipmi PIC, ale nasledujúce pozorovania odhaľujú možné obmedzenia/problémy s kompatibilitou/chyby?

- Dlhý čas nábehu MCLR, zatiaľ čo C2 sa nabíja do VPP v prvom impulze TX. Nezodpovedá špecifikácii 3.

- Sériový port nabíja C2, keď TX stúpne a RTS klesne. RTS má ale aj úlohu nabíjať C3. Ak dôjde k obom súčasne, vytvára to vyššie zaťaženie RTS, v dôsledku čoho C3 pri simulácii stráca nabíjanie (VSS stúpa) po 2 ms. Nezodpovedá špecifikácii 1.

- C3 sa vybíja (VSS začne stúpať) po tom, ako sa hodinové impulzy zastavia na 3,5 ms.

- Aký je účel C2, je vôbec potrebný?

Riešenia

- PICPgm pravdepodobne používa softvérový „pracovný kruh“. Na prednabitie na C2 musí použiť dlhý TX impulz, potom až po druhom TX impulze vstúpiť do programovacieho režimu? Na simuláciu som znížil hodnotu C2 na 1uF, aby som poskytol čas nábehu 1 ms. Nie je to ideálne riešenie.

- Rozdeľte C2 a C3 tak, aby sa nabíjali nezávisle. Jedna malá modifikácia JDM2, C2 sa odkazuje na GND namiesto VSS.

- Vyriešil JDM3. ICSP je oveľa spoľahlivejší, pretože PIC je napájaný cieľovým obvodom.

- JDM4 rieši problém 1. Jedná sa o jednoduchý dizajn, ktorý úplne eliminuje C2.

Krok 9: A nakoniec

Dôkaz pudingu je v jedení. Tento JDM funguje, takže ho naďalej používajte.

A moje odporúčania sú:

- použite JDM2 na programovanie zásuviek a sériové porty 12V,

- použite JDM4 pre programátor ICSP a sériové porty nad +/- 9V,

- použite JDM4 s prepojkou X2 odstránenou pre sériové porty nad +/- 7V.

Referencie:

Korenie Analog Devices LT

picpgm

Fruttenboel

Sledujte ďalšie projekty PIC na sly-corner

Odporúča:

Súprava Elegoo Super Started Uno R3 Recenzia: 4 kroky

Elegantoo Super Started Kit Uno R3 Recenzia: Pred niekoľkými dňami mi Elegoo poslal na testovanie túto Super Starter Kit. Pozrime sa teda, čo je vo vnútri. Pri otváraní tohto kompaktného puzdra vidíme veľa vecí. Na obálke je register so všetkými komponentmi. Vnútri máme poďakovanie so všetkým

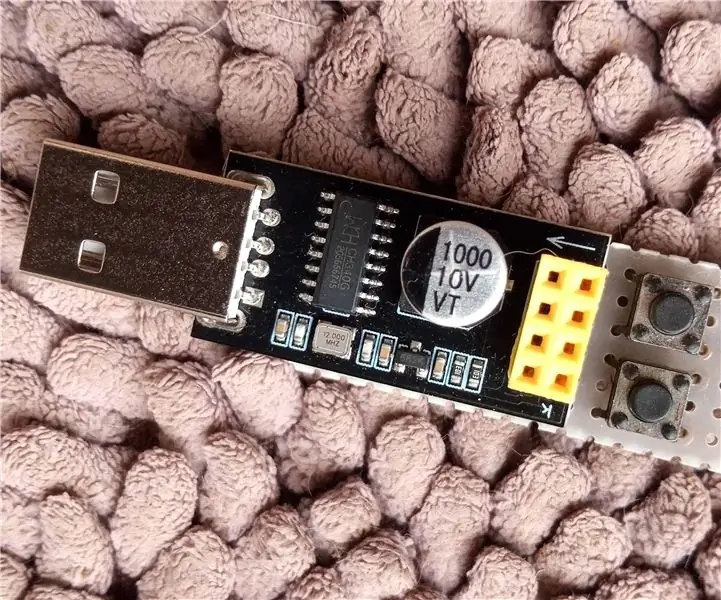

Hack programátora ESP -01 - jednoduchý :): 6 krokov

Programátorský hack ESP-01-jednoduchý :): Ahoj ESPers, v tomto návode vám ukážem jednoduchý hack, ako vytvoriť programátor pre modul ESP-01 / ESP8266-01 / ES-01. Väčšina z nás použila ako programátory tohto modulu dosku Arduino alebo zariadenia FTDI USB-TTL. Obe metódy fungujú dobre. Ale t

Ako flashovať alebo naprogramovať firmvér ESP8266 AT pomocou blikača a programátora ESP8266, modulu IOT Wifi: 6 krokov

Ako flashovať alebo naprogramovať firmvér ESP8266 AT pomocou blikača a programátora ESP8266, modulu IOT Wifi: Popis: Tento modul je adaptér /programátor USB pre moduly ESP8266 typu ESP-01 alebo ESP-01S. Je vhodne vybavený zásuvkou 2 x 4P 2,54 mm na zapojenie ESP01. Tiež vylamuje všetky piny ESP-01 prostredníctvom mužského konektora 2x4P 2,54 mm

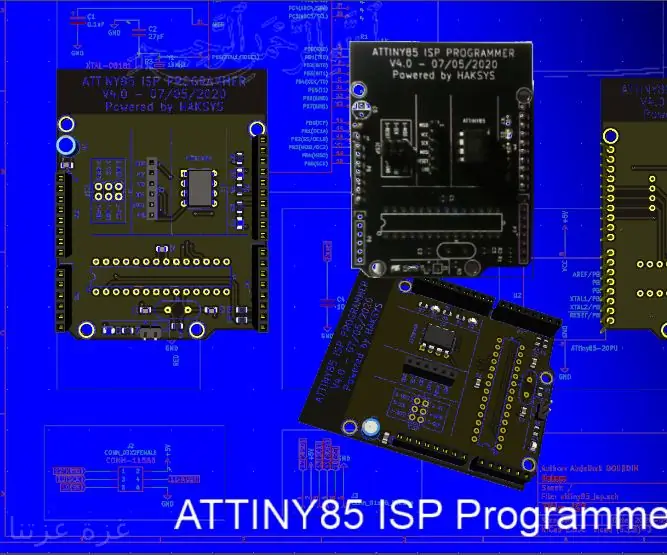

Ešte ďalší štít programátora ATTINY85 ISP pre Arduino: 8 krokov

Ešte ďalší štít programátora ATTINY85 ISP pre Arduino: م الله الرحمن الرحيم Programátorský štít ATTINY85 ISP je navrhnutý tak, aby sa dal ľahko naprogramovať ovládače ATTiny85 µ. Štít musí byť zapojený do dosky Arduino Uno. Arduino Uno je pripravený pôsobiť ako ∈ Sériový programátor &"

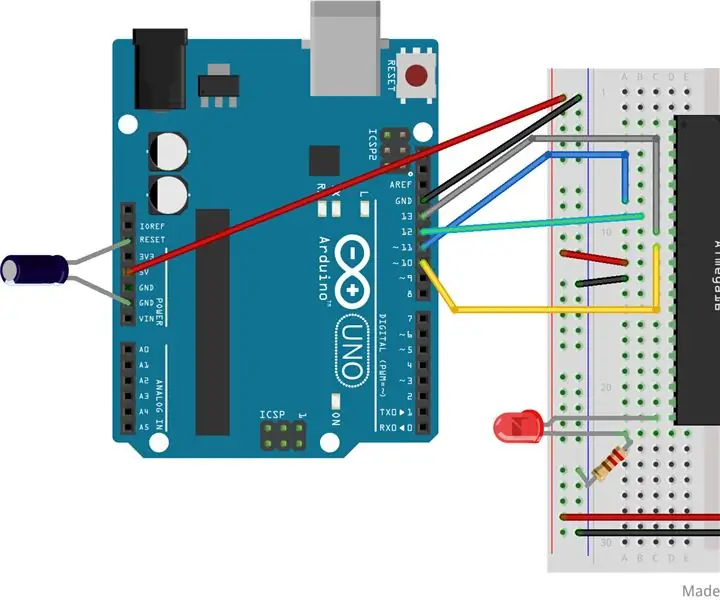

Ako nahrať C kód do ِ AVR pomocou Arduino Uno ako programátora: 6 krokov

Ako nahrať C kód do ِ AVR pomocou Arduino Uno ako programátor: AHOJ všetci: D Tu sa podelím o jednoduchý spôsob, ako naprogramovať akýkoľvek AVR čip pomocou Arduino Uno R3 Všetko, čo potrebujete na napálenie kódu do svojho mikrokontroléra, je Arduino Uno namiesto nákupu konkrétneho. programátor, ktorý stojí veľa