Obsah:

- Krok 1: Blokový diagram

- Krok 2: Princíp činnosti

- Krok 3: Implementácia logiky

- Krok 4: Vyriešenie zablokovania

- Krok 5: Konfigurácia zariadenia - obvod Matrix0

- Krok 6: Konfigurácia zariadenia - Logika hodín SPI

- Krok 7: Konfigurácia zariadenia - vlastnosti komponentov Matrix0

- Krok 8: Konfigurácia zariadenia - obvod Matrix1

- Krok 9: Konfigurácia zariadenia - 3 -bitové binárne počítadlo

- Krok 10: Konfigurácia zariadenia - 3 -bitová porovnávacia logika

- Krok 11: Konfigurácia zariadenia - digitálna porovnávacia logika a dočasný register

- Krok 12: Konfigurácia zariadenia - vlastnosti komponentov Matrix1

- Krok 13: Výsledky

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:57.

- Naposledy zmenené 2025-01-23 15:05.

Riadiace systémy a súvisiace zariadenia pracujú s viacerými zdrojmi energie, ako sú predpäté vedenia alebo batérie, a musia sledovať najvyššie (alebo najnižšie) vedenie v rámci danej sady.

Napríklad prepínanie záťaže v systéme napájanom z „viacerých batérií“vyžaduje, aby systém monitoroval buď minimálne alebo maximálne napätie v poli batérií (max alebo min ako funkcia konkrétneho spínacieho algoritmu) a dynamicky smeroval záťaž do najvhodnejší zdroj v reálnom čase. Alternatívne môže byť pre správne nabíjanie systému potrebné dočasne odpojiť batériu s najnižším napätím.

Ďalším príkladom je moderný solárny systém, kde je každý solárny panel vybavený tiltrotačným mechanizmom a obvodom na sledovanie slnečného žiarenia (druhý poskytuje informácie o polohe Slnka na orientáciu panelu). S informáciami o maximálnom napätí je možné každú polohu solárneho panelu doladiť na základe toho, že panel reťazca skutočne dodáva najvyššie výstupné napätie, čím sa dosiahne vynikajúca úroveň optimalizácie výkonu.

Existuje niekoľko rôznych značiek komerčných integrovaných obvodov (hlavne mikrokontroléry), ktoré v zásade môžu implementovať sledovač maximálneho napätia. Vyžadujú však programovanie a sú menej nákladovo efektívne ako riešenie so zmiešaným signálom. Doplnenie dizajnu Dialog GreenPAKTM môže pozitívne ovplyvniť cenovú dostupnosť, veľkosť a modularitu dizajnu. Tento dizajn využíva výhodu integrácie analógových aj digitálnych obvodov do jedného čipu.

V tomto návode je implementovaný analógový front-end a digitálna logika potrebná na implementáciu vyhľadávača max. (Alebo prípadne minimálneho) napätia medzi osem rôznych zdrojov.

Na implementáciu 8-kanálového analógového monitora napätia max/min sa používa SLG46620G.

Ďalej sme popísali potrebné kroky, aby ste pochopili, ako bolo riešenie naprogramované na vytvorenie 8-kanálového analógového monitora napätia max/min. Ak však chcete získať iba výsledok programovania, stiahnite si softvér GreenPAK a zobrazte už dokončený súbor návrhu GreenPAK. Pripojte vývojovú súpravu GreenPAK k počítaču a spustením programu vytvorte 8-kanálový analógový monitor maximálneho/minimálneho napätia.

Krok 1: Blokový diagram

Obrázok 1 zobrazuje globálny diagram implementovaného systému.

Reťazec až 8 zdrojov s premenlivým napätím je multiplexovaný a prepojený s ADC modulom GreenPAK pripojeným k prispôsobenému vnútornému dizajnu, ktorý je schopný vybrať zdroj s najvyšším napätím vzhľadom na ostatné. Interná logika vydáva tieto informácie na zobrazenie alebo ďalšie spracovanie.

Dizajn je založený na produkte GreenPAK SLG46620G, pretože obsahuje všetky potrebné analógové a digitálne stavebné prvky pre aplikáciu. V tejto implementácii je pole skenované pomocou analógového multiplexora ADG508 priamo poháňaného integrovaným obvodom GreenPAK.

Výstupnou informáciou je 3-bitové digitálne číslo zodpovedajúce číslu zdroja napätia pri maximálnom napätí. Priamy spôsob, ako získať tieto informácie, je zobraziť číslo na 7-segmentovom displeji. To sa dá ľahko dosiahnuť prepojením digitálneho výstupu SLG46620G so 7-segmentovým ovládačom displeja, ako je riešenie GreenPAK popísané v Referencii alebo so spoločným 74LS47 IC.

Prezentovaný obvod hľadá maximálne napätie. Aby sa návrh zmenil na vyhľadávač minimálneho napätia, musí byť medzi analógový multiplexor a analógový vstup GreenPAK pridaný jednoduchý predkondicionovací obvod, ktorý odčíta výstup multiplexora od referenčného napätia 1 V.

Krok 2: Princíp činnosti

Cieľom návrhu je vybrať zdroj s maximálnym napätím, a preto sa vykoná skenovanie v celom poli, pričom sa uloží posledná maximálna hodnota a porovná sa s ďalšou hodnotou na vstupe (ktorá patrí k ďalšiemu zdroju napätia v skenovaní).

V nasledujúcom texte budeme odkazovať na kompletnú sekvenciu multiplexovania pozdĺž všetkých vstupov ako „skenovanie“alebo „slučka“.

Porovnanie dvoch hodnôt sa neuskutočňuje pomocou komponentov ACMP (je však k dispozícii v SLG46620G), ale skôr pomocou modulu DCMP, akonáhle sú hodnoty digitalizované. Toto je pokročilá a zdokonalená technika, ktorej sa najskôr venujeme v Referencii.

Obrázok 2 ukazuje, ako je SLG46620G štruktúrovaný pre tento dizajn.

Analógový vstupný signál prechádza na vstup ADC prostredníctvom komponentu PGA s nastaveným ziskom 1. Možné sú aj rôzne nastavenia zosilnenia, aby sa našiel najlepší súlad s prednou koncovou elektronikou určenou na mapovanie vstupných napätí na 0-1 V rozsah modulu GreenPAK ADC.

ADC pracuje v režime s jedným koncom a prevádza analógový signál na 8-bitový digitálny kód, ktorý sa potom prenesie do modulu DCMP. Digitálny kód je tiež vložený do bloku SPI, nakonfigurovaného ako vyrovnávacia pamäť ADC/FSM, kde je možné uložiť digitálny kód a nezmení sa, kým na vstup SPI CLK nepríde ďalší impulz. Všimnite si, že vyhradený logický blok riadi vstup SPI CLK. Túto časť preskúmame neskôr, pretože ide o „základnú“logiku zodpovednú za správnu funkciu. Nový digitálny kód je uložený do modulu SPI iba vtedy, ak patrí k skutočnému maximálnemu vstupnému napätiu.

Komponent DCMP sa používa na porovnanie aktuálnych údajov ADC s posledným víťazom (to je posledné nájdené maximum), ktorý je uložený v bloku SPI. Generuje impulz na výstupe OUT+, keď sú nové údaje ADC väčšie ako predchádzajúce. Signál OUT+ používame na aktualizáciu bloku SPI s novým víťazom.

Globálny hodinový signál poháňa konverzie ADC a všeobecné časovanie. Akonáhle je konverzia vykonaná, výstupné signálne signály ADT ADC, koordinované v čase s paralelným dátovým výstupom ADC. Výstup INT používame aj na zvýšenie 3-bitového binárneho počítadla implementovaného DFF v Matrix1, čo je užitočné z troch dôvodov:

1. Výstupné vedenia počítadla adresujú externý analógový multiplexor, čím slúžia ďalšiemu vstupnému napätiu do ADC;

2. počet sa zmrazí do 3-bitového registra (implementovaného v Matrix1), aby sa počas skenovania uložil dočasný víťaz;

3. Počet sa dekóduje, aby sa aktualizoval druhý 3-bitový register (implementovaný v Matrix0) po dokončení skenovania.

Krok 3: Implementácia logiky

Modul ADC postupne poskytuje prevádzané údaje všetkých vstupných napätí, jeden po druhom, neobmedzene dlho. Akonáhle je multiplexor adresovaný 0b111 (desatinne 7), počítadlo sa zroluje na 0b000 (desatinné 0), čím začne nové skenovanie vstupných napätí.

Keď je paralelný dátový výstup platný, počas skenovania sa generuje výstupný signál ADC INT. Keď tento signál pulzuje, analógový multiplexor sa musí prepnúť na ďalší vstup, pričom poskytne PGA zodpovedajúce napätie. Preto je výstup ADC INT priamym hodinovým signálom 3-bitového binárneho počítadla z obrázku 2, ktorého 3-bitové paralelné výstupné slovo priamo adresuje externý analógový multiplexor („V výber“na obrázku 1).

Teraz sa pozrime na príklad, kde majú vstupné napätia mať nasledujúce vzťahy:

a) V0 <V1 <V2

b) V2> V3, V4

c) V5> V2

Obrázok 3 predstavuje hlavné signály zapojené do mechanizmu maximálneho rozhodovania.

Pretože dáta sú nakoniec taktované do registra vyrovnávacej pamäte SPI synchrónne s impulzmi INT, existuje porovnávacie okno, kde je obsah vyrovnávacej pamäte SPI porovnávaný s ďalším výsledkom prevodu ADC. Toto konkrétne načasovanie má za následok generovanie impulzov OUT+ na výstupe DCMP. Tieto impulzy môžeme využiť na načítanie nových hodnôt do registra vyrovnávacej pamäte SPI.

Ako je zrejmé z riadka údajov vyrovnávacej pamäte SPI na predchádzajúcom obrázku, register SPI vždy obsahuje čas od času najväčšiu hodnotu medzi 8 vstupmi a aktualizuje sa iba vtedy, keď modul DCMP zistí väčšiu hodnotu (odkaz na DCMP) OUT+ výstupný riadok grafu, chýbajúce impulzy spôsobia, že V2 zostane v registri zaistený, kým sa porovná s V5).

Krok 4: Vyriešenie zablokovania

Ak by implementovaná logika bola taká, ako je popísané vyššie, je zrejmé, že by sme narazili na zablokovanie: systém je schopný detekovať iba vyššie napätie, ako je napätie zodpovedajúce tomu, čo je uložené v registri vyrovnávacej pamäte SPI.

To platí aj v prípade, že by sa toto napätie znížilo a potom by sa iný vstup, doteraz nižší ako ten, stal najvyšším: nikdy by sa nezistil. Táto situácia je lepšie vysvetlená na obrázku 4, kde sú prítomné iba 3 vstupné napätia kvôli jasnosť.

V čase iterácie 2 V3 klesá a V1 je skutočné maximálne napätie. Modul DCMP však neposkytuje impulz, pretože údaje uložené v registri vyrovnávacej pamäte SPI (zodpovedajúce 0,6 V) sú väčšie ako údaje zodpovedajúce V1 (0,4 V).

Systém sa potom správa ako „absolútny“maximálny vyhľadávač a neaktualizuje výstup správne.

Pekný spôsob, ako tento problém prekonať, je vynútiť opätovné načítanie údajov do registra vyrovnávacej pamäte SPI, keď systém dokončí celý cyklus dotazovania všetkých kanálov.

V skutočnosti, ak je napätie na tomto vstupe stále najvyššie, nič sa nezmení a ovládanie bezpečne pokračuje (s odkazom na obrázok 4 vyššie, toto je prípad iterácií slučky 0 a 1). Na druhej strane, ak sa napätie na tomto vstupe náhodou zníži na hodnotu menšiu ako iný vstup, potom opätovné načítanie hodnoty poskytne modulu DCMP možnosť vytvoriť impulz OUT+ pri porovnaní s novou maximálnou hodnotou (to je prípad opakovania slučiek 2 a 3).

Na prekonanie problému je potrebný kus logického obvodu. Keď slučka dosiahne skutočný maximálny vstup, musí generovať hodinový signál pre komponent SPI, čím si vynúti opätovné načítanie svojho aktualizovaného dátového slova do registra vyrovnávacej pamäte SPI. Toto bude prediskutované v častiach 7.2 a 7.6 nižšie.

Krok 5: Konfigurácia zariadenia - obvod Matrix0

SLG46620G má dva maticové bloky, ako je znázornené na obrázku 2. Nasledujúce obrázky znázorňujú príslušné konfigurácie zariadení.

Horná časť obvodu je „slučkový register“realizovaný s 3 DFF (DFF0, DFF1 a DFF2). Po každej slučke vstupného multiplexora sa obnoví, aby sa do 7-segmentového ovládača displeja odoslalo binárne číslo „víťaz“, tj vstup s najvyšším napätím v poslednom skenovaní. Hodiny do DFF a údaje pochádzajú z logiky implementovanej v Matrix1 prostredníctvom portu P12, P13, P14 a P15.

Dolná časť je analógový predný koniec so vstupom na pine 8 a PGA so ziskom x1. Výstup ADC INT smeruje k taktovacej logike SPI aj k Matrix1 cez port P0, kde bude slúžiť ako hodinový signál pre implementované počítadlo.

Paralelné dátové výstupy ADC a SPI sú označené NET11 a NET15 a majú sa pripojiť k komponentu DCMP v Matrix1.

Krok 6: Konfigurácia zariadenia - Logika hodín SPI

Ako už bolo uvedené v časti „Implementácia logiky“, register vyrovnávacej pamäte SPI sa aktualizuje zakaždým, keď porovnanie medzi skutočnou uloženou hodnotou a novými údajmi o konverzii ADC generuje impulz na výstupe DCMP OUT+.

Integrita signálu je zaistená, ak je tento signál AND-ed s výstupom ADC INT. Tým sa zabráni akýmkoľvek špičkám a falošnému spusteniu.

Tiež sme zdôraznili, že na preskočenie zablokovania je potrebné aktualizovať vyrovnávaciu pamäť SPI, keď slučka dosiahne údaje o skutočnom víťazovi.

V hre o správne taktovanie SPI sú potom tri signály:

1. Výstup ADC INT (LUT0-IN1)

2. Výstup DCMP OUT+ (LUT0-IN0 cez port P10)

3. Počet sa rovná signálu západky (LUT0-IN2 cez port P11)

Prvé dva sú vydané AND a oba OR vydané s týmto druhým v LUT0, ktorého implementácia je nakonfigurovaná ako na obrázku 6.

Krok 7: Konfigurácia zariadenia - vlastnosti komponentov Matrix0

Obrázky 7-10 zobrazujú zostávajúce okná vlastností komponentov patriace do Matrix0.

Krok 8: Konfigurácia zariadenia - obvod Matrix1

Krok 9: Konfigurácia zariadenia - 3 -bitové binárne počítadlo

Horná časť obvodu obsahuje logické prvky, hlavne 3-bitový binárny čítač taktovaný výstupom ADC INT, ako už bolo uvedené. Toto počítadlo je implementované s celkom „štandardnou“schémou znázornenou na obrázku 12.

Toto počítadlo je v našom návrhu realizované pomocou žabiek DFF9, DFF10, DFF11 a INV1, LUT4, LUT8. Výstup DFF9 je LSB, zatiaľ čo DFF11 je MSB, ako je znázornené na obrázku 13.

LUT4 je nakonfigurovaný ako XOR, zatiaľ čo LUT8 vykonáva logiku AND-XOR na obrázku 12.

Výstupy počítadla prechádzajú na tri digitálne výstupné piny na adresu externého analógového multiplexora.

LUT10 dekóduje kód počítadla, keď je skenovanie dokončené, a napája impulz do Matrix0 cez DLY8 a port P12. To sa jednoducho dosiahne AND-ovaním výstupov počítadla, čím sa dekóduje číslo 7 dec (0b111 binárne, koniec slučky).

Krok 10: Konfigurácia zariadenia - 3 -bitová porovnávacia logika

Obrázok 15 zobrazuje obvod použitý na detekciu, keď sa slučka iteruje na aktuálnej adrese „víťaz“. V tomto prípade, ako už bolo diskutované, digitálny impulz by mal vynútiť opätovné načítanie aktuálneho výsledku ADC, aby sa vyriešila možná situácia zablokovania.

Adresa „víťaz“je uložená v dočasnom registri Matrix1 (pozri nižšie), zatiaľ čo aktuálnu adresu vydáva binárne počítadlo.

Brány XNOR poskytujú skutočný (logický 1 alebo „vysoký“) výstup, ak sú obidva vstupy rovnaké. A-tento signál pre všetky bity (LUT9) nám dáva impulz, keď sú oba binárne kódy rovnaké. Podrobnosti o bránach XOR ako kontrole parity nájdete v Referencii.

Signál „Counter-equals-Latch“je odoslaný do Matrix0 cez port P11.

Krok 11: Konfigurácia zariadenia - digitálna porovnávacia logika a dočasný register

Spodná časť obrázku 11 (zvýraznená na obrázku 16) zobrazuje blok DCMP, časť rozhodovania tohto návrhu.

DFF6, 7 a 8 tvoria 3-bitový register na uloženie dočasného vstupného čísla „víťaz“, keď je slučka spustená. Vstupom do klopných obvodov sú 3-bitové binárne výstupy čítača, ako je vidieť v globálnom obvode Matrix1 na obrázku 11, ktoré tu boli kvôli prehľadnosti vynechané.

Výstupy z tohto registra nemôžu poháňať priamo 7-segmentový displej, pretože tu uložená hodnota sa počas skenovania mení a mala by byť považovaná za „platnú“až na konci samotného skenovania.

Z tohto dôvodu sa výstupy dočasných registrov pripájajú k slučkovému registru Matrix0 prostredníctvom intermaticových portov P13, P14 a P15.

Na obrázku 16 je dôležité pozorovať, že dočasný register je taktovaný výstupom DCMP OUT+, keď výsledkom porovnania registrov ADC-SPI je nové nájdené maximum.

Rovnaký signál OUT+ je prenášaný do Matrix0, SPI CLK Logic, cez port P10.

Krok 12: Konfigurácia zariadenia - vlastnosti komponentov Matrix1

Obrázky 17-19 ukazujú okná vlastností komponentov patriace do Matrix1.

Krok 13: Výsledky

Na testovanie implementácie bol skonštruovaný prototyp hodnotiacej dosky, kde je 8 analógových vstupných napätí získaných sériou odporových deličov s TrimPots (ako je znázornené na obrázku 20).

Použitý multiplexor je ADG508, časť, ktorá môže pracovať s jediným napájaním (12 V).

7-segmentový ovládač displeja je 74LS47. Dekóduje paralelné vstupné slovo a priamo poháňa 7-segmentový displej so spoločnou anódou.

Hodnotiaca doska má 2x10 pravouhlý konektor, ktorý je možné pripojiť priamo k rozšírenej vývojovej platforme GreenPAK na jej rozširujúcom konektore, ako je znázornené na obrázku 21.

V spojení s platformou GreenPAK Advanced Development Platform je veľmi jednoduché vykonávať merania signálov na rýchlu kontrolu. Na obrázku 22 je napríklad znázornená sada signálov (respektíve výstupov CLOCK, ADC INT a výstup DCMP OUT+) zachytených logickým analyzátorom HP 54620A. Krivky sú spúšťané stúpajúcou hranou signálu OUT+ (na rozsahu označenom ako „A> B“), a preto ide o zachytenie tvaru vlny, keď je medzi analógovými vstupmi detekované nové maximálne napätie. V skutočnosti to bolo získané otáčaním jedného z TrimPotov hodnotiacej rady na zvýšenie zodpovedajúceho napätia zobrazeného na obrázku 22.

Obrázok 23 zobrazuje schému hodnotiacej rady.

Záver

V tomto návode sme implementovali osemkanálový vyhľadávač maximálneho (alebo minimálneho) napätia, ktorý sa má používať ako spoločný doplnok viackanálových riadiacich systémov. Prezentovaný prístup využíva pokročilé funkcie komponentov GreenPAK a ukazuje, ako je možné integrovať do jedného čipu analógové a digitálne funkcie. Niekoľko komerčných integrovaných obvodov je možné nahradiť Dialog GreenPAK, aby bolo možné znížiť veľkosť aplikácie a náklady.

Odporúča:

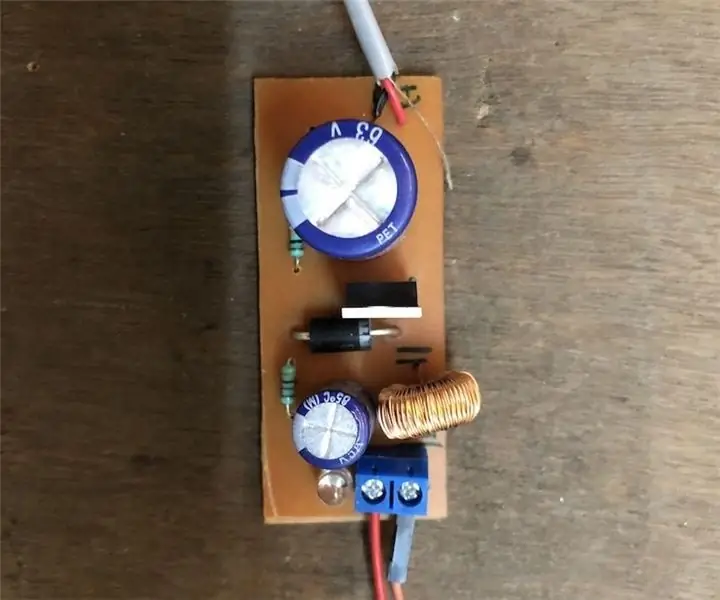

DIY vreckový merač napätia DC: 5 krokov

DIY vreckový merač napätia DC: V tomto návode vám ukážem, ako si vyrobiť vreckový merač jednosmerného napätia DIY s piezovým bzučiakom na kontrolu obvodu sami. Všetko, čo potrebujete, je základná znalosť elektroniky a trochu času. Ak máte akékoľvek otázky alebo problémy, môžete

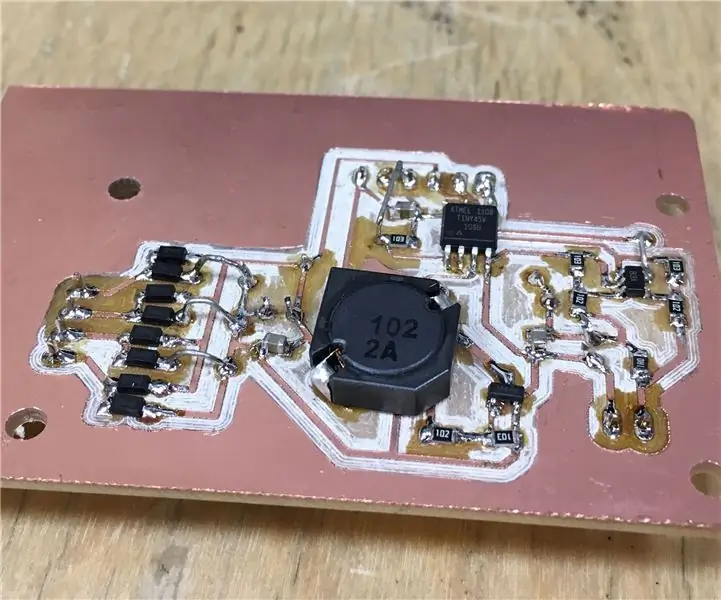

Monitor napätia pre vysokonapäťové batérie: 3 kroky (s obrázkami)

Monitor napätia pre vysokonapäťové batérie: V tejto príručke vám vysvetlím, ako som postavil monitor napätia batérie pre svoj elektrický longboard. Namontujte ho, ako chcete, a k batérii (GND a VCC) pripojte iba dva vodiče. Táto príručka predpokladala, že napätie vašej batérie presiahne 30 voltov,

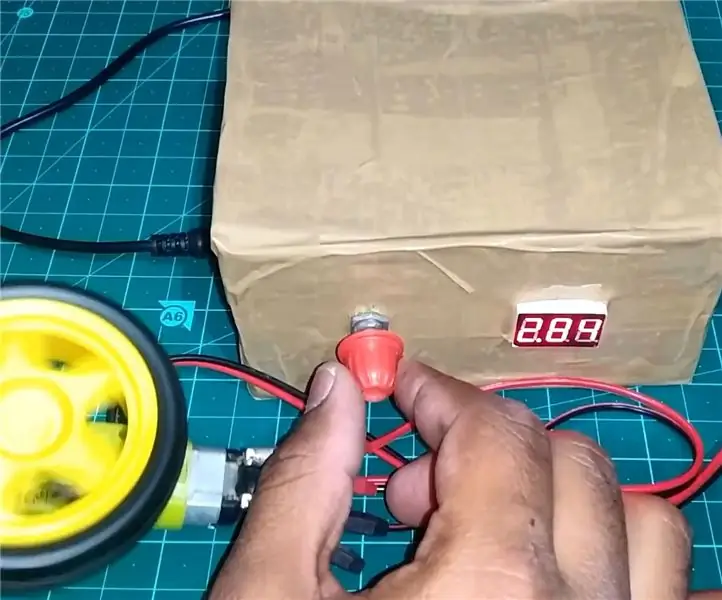

Menič napätia DC - DC prepínaného režimu Buck napätia (LM2576/LM2596): 4 kroky

Prevodník napätia DC-DC prepínača režimu znižovania napätia (LM2576/LM2596): Výroba vysoko efektívneho prevodníka dolárov je náročná práca a dokonca aj skúsení inžinieri vyžadujú niekoľko návrhov, aby prišli na ten správny. je menič napätia DC na DC, ktorý znižuje napätie (pri zvyšovaní

Sledovač maximálneho výkonu pre malé veterné turbíny: 8 krokov

Nástroj na sledovanie maximálneho výkonu pre malé veterné turbíny: Na internete je veľa kutilových veterných turbín, ale len málo z nich jasne vysvetľuje výsledok, ktorý získavajú z hľadiska výkonu alebo energie. Tiež často dochádza k zámene medzi silou, napätím a prúdom. Ľudia často hovoria: „Meral som

DIY napájací zdroj pomocou LM317 - Výstup variabilného napätia Lm 317: 12 krokov

DIY napájací zdroj pomocou LM317 | Výstup premenlivého napätia Lm 317: Dnes sa naučíme, ako vytvoriť malú napájaciu jednotku pre vaše malé projekty. LM317 bude dobrou voľbou pre nízkonapäťové napájanie. Lm317 poskytuje premenlivé výstupné napätie, ktoré závisí od skutočne pripojenej hodnoty odporu s