Obsah:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:57.

- Naposledy zmenené 2025-01-23 15:05.

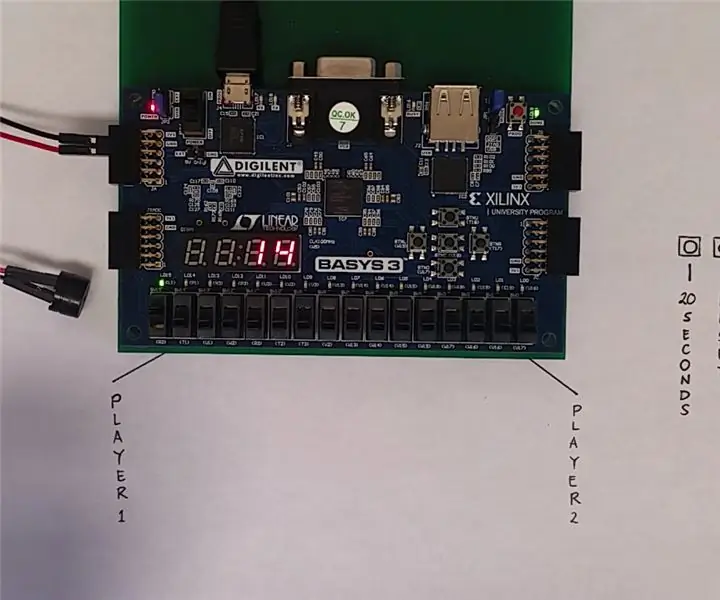

Konkurenčný bzučiakový systém navrhnutý v tomto projekte funguje podobne ako bzučiakové systémy používané v regionálnych a národných súťažiach Bowl of Science. Tento projekt bol inšpirovaný mojím trojročným zapojením do vedeckého misského tímu mojej strednej školy. Vždy sme mali túžbu obnoviť systém blokovacieho bzučiaka s 5-sekundovým a 20-sekundovým časovačom.

Aby poskytli určité pozadie v systéme bzučiakov, bzučiaky vedeckých misiek sú naprogramované tak, aby zadávali maximálne 8 hráčov (s 8 samostatnými bzučiakmi). Hneď ako stlačíte jeden bzučiak, rozsvieti sa bzučiak prvej osoby, ktorý hráč dostane otázku. Ostatní hráči budú „zablokovaní“, čo znamená, že ich bzučiaky nebudú reagovať, kým moderátor nevynuluje systém bzučiakov.

Potom, čo si moderátor prečíta otázky, stlačením tlačidla spustí časovač odpočítavania, ktorý sa zobrazí na sedemsegmentovom displeji. Po otázke „zahodenie“môže moderátor stlačením pravého tlačidla začať odpočítavanie od 5 sekúnd. Medzitým, po „bonusovej“otázke, môže moderátor stlačením ľavého tlačidla začať odpočítavanie od 20 sekúnd. Akonáhle časovač dosiahne nulu, zvukový signál oznámi, že hráčovi došiel čas.

Ak chcete resetovať systém a časovač odpočítavania, moderátor môže stlačiť stredné tlačidlo. Ak chcete resetovať mechanizmus blokovania a kontrolky LED prehrávača, prepínače pre hráča 1 a hráča 2 musia byť zapnuté.

Krok 1: Materiály

Budete potrebovať nasledujúce:

- Doska Basys3 (alebo ekvivalentná doska FPGA)

- Micro-B USB kábel

- Reproduktor (použil som pasívny reproduktor)

- 2 drôty

- Softvér na implementáciu na FPGA (použil som Vivado)

- Súbor systému Competitive Buzzer System

Krok 2: Diagram čiernej skrinky

Schéma čiernej skrinky zobrazuje vstupy a výstupy, ktoré budú použité v tomto systéme bzučiakov.

VSTUPY:

player1, player2 Tieto vstupy sú pripojené k dvom prepínačom na doske Basys3. Pre pohodlie budú použité spínače úplne vľavo a vpravo.

reset Stredné tlačidlo bude slúžiť ako tlačidlo resetovania.

count_down_20_sec Ľavé tlačidlo bude slúžiť na zobrazenie 20-sekundového tlačidla časovača.

count_down_5_sec Pravé tlačidlo bude predstavovať 20-sekundové tlačidlo časovača. Aby ste zaistili spustenie 20-sekundového aj 5-sekundového časovača, podržte tlačidlo, kým sa sedemsegmentový displej nezobrazí.

CLK Doska FPGA vygeneruje hodiny, ktoré bežia s frekvenciou 10 ns.

VÝSTUPY:

reproduktor Výstup reproduktora je pripojený k externému bzučiaku alebo reproduktoru. Reproduktor budete musieť pripojiť k portom JA pmod na doske Basys3. Tento krok bude popísaný nižšie.

reproduktor_LED Tento výstup je pripojený k dióde LED v strede dosky a bude iba indikovať, kedy je výstup reproduktorov FPGA vysoký. Môžete to použiť na testovanie externého reproduktora. Upozorňujeme, že niektoré porty pmod nemusia správne fungovať, takže môžete vyskúšať rôzne a pomocou diódy LED skontrolovať, či by mal byť reproduktor zapnutý.

SEGMENTY Tento výstup je spojený s ôsmimi jednotlivými segmentmi na sedemsegmentovom displeji vrátane desatinnej čiarky.

DISP_EN Tento výstup je pripojený k štyrom anódam na sedemsegmentovom displeji.

player_LED Tento výstup je 2-zväzkový signál, ktorý je pripojený k LED diódam nad prepínačmi player1 a player2. Prvý hráč, ktorý otočí príslušný spínač, bude indikovaný diódou LED. Upozorňujeme, že obe diódy LED nemôžu svietiť súčasne.

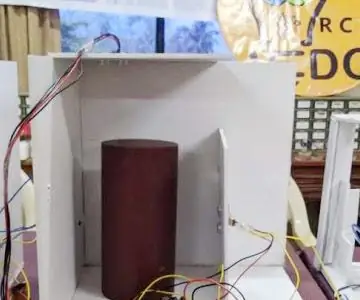

Krok 3: Pripojenie externého reproduktora

Ak chcete pripojiť externý reproduktor k doske Basys3, vezmite dva vodiče a zapojte ich podľa obrázka vyššie. Biela čiara spája záporný pól reproduktora s uzemňovacím portom na doske. Červená čiara spája kladný pól reproduktora s portom JA10 pmod na doske.

Súbor obmedzení je navrhnutý tak, aby fungoval akýkoľvek port od JA1 do JA10. Niektoré kolíky na doske však nereagujú, takže ak JA10 nefunguje, môžete skúsiť ostatné porty.

Krok 4: Štrukturálny diagram

Obrázok vyššie ukazuje štruktúrny diagram konkurenčného bzučiakového systému vrátane všetkých komponentov, ktoré tvoria hlavný modul. Ich popis je nasledujúci:

player_lockout_LED1 LED dióda uzamknutia prehrávača je stroj s konečným stavom, ktorý používa kódovanie jedným spustením. Má štyri vstupy: player1, player2, reset a CLK. Obsahuje výstup 2-bitového zväzku player_LED. Vstupy a výstupy komponentu player_lockout_LED1 sú všetky priamo pripojené k rovnako pomenovaným vstupom a výstupom hlavného modulu.

buzzer_tone1 Komponent bzučiaka je založený na tomto kóde uverejnenom na fóre

stackoverflow.com/questions/22767256/vhdl-… Bol však upravený tak, aby poskytoval nepretržitý zvuk s frekvenciou 440 Hz (poznámka). Povolovací vstup je pripojený k signálu bzučiakom_povoliteľnému, ktorý je výstupom komponentu down_counter_FSM1.

clk_div1 Časť oddeľovača hodín je upravenou verziou rozdeľovača hodín profesora Bryana Mealyho, ktorý je k dispozícii na PolyLearn. Spomaľuje hodiny, takže výstupná perióda je 1 sekunda.

down_counter_FSM1 Počítadlo nadol je FSM navrhnuté tak, aby odpočítavalo až do nuly. Dva možné časy spustenia sú 20 alebo 5, ktoré zvolí používateľský vstup. Keď časovač dosiahne nulu, vydá „1“, čo znamená, že čas uplynul. Tento výstup slúži ako povolenie pre komponent tónu bzučiaka. Počítadlo tiež vysiela signál 8-bitového zväzku, ktorý odosiela 8-bitový BCD, ktorý je odoslaný do segmentového dekodéra. Ďalším výstupom je counter_on, ktorý je tiež pripojený k platnému vstupu na segmentovom dekodéri.

sseg_dec1 Sedemsegmentový dekodérový komponent je k dispozícii na PolyLearn a napísal ho profesor Bryan Mealy. Využíva vstup BCD poskytovaný serverom down_counter_FSM1 a vydáva desatinné číslo na sedemsegmentovom displeji. Keď je počítadlo zapnuté, platný vstup je vysoký. To umožňuje dekodéru zobrazovať desatinné číslo na sedemsegmentovom displeji. Keď je počítadlo vypnuté, platný vstup je nízky. Sedemsegmentový displej potom zobrazí iba štyri čiarky.

Krok 5: Diagram stroja s konečným stavom (FSM)

Zoznam citlivosti pre konečný automat obsahuje player1, player2, reset a hodiny. Výstup FSM je 2-bitový zväzkový prehrávač_LED pripojený k dvom diódam LED na doske Basys3. Stroj konečných stavov zobrazuje nasledujúce tri stavy:

ST0 je počiatočný stav. V tomto stave sú dve LED diódy vypnuté. FSM zostane v tomto stave, ak sú player1 aj player2 na nízkej úrovni. Asynchrónny reset tiež nastaví stav na ST0. Keď je prepínač player1 nastavený na vysokú úroveň, ďalším stavom bude ST1. Ak je prepínač player2 nastavený na vysokú úroveň, ďalším stavom bude ST2.

ST1 je stav, pre ktorý svieti LED dióda player1. FSM zostane v tomto stave pre všetky vstupy. To znamená, že aj keď je prepínač player2 nastavený na vysokú hodnotu bezprostredne potom, čo je spínač player1 vysoko, zostane v ST1. Iba asynchrónny reset môže nastaviť nasledujúci stav na ST0.

ST2 je stav, pre ktorý svieti dióda LED player2. Podobne ako ST !, FSM zostane v tomto stave pre akýkoľvek vstup, aj keď je prepínač player1 nastavený na vysokú bezprostredne po tom, čo je prepínač player2 vysoko. Opäť platí, že iba asynchrónny reset môže nastaviť nasledujúci stav na ST0.

Odporúča:

Domáci automatizačný systém WiFi s extrémne nízkym výkonom: 6 krokov (s obrázkami)

Domáci automatizačný systém WiFi s extrémne nízkym výkonom: V tomto projekte vám ukážeme, ako môžete v niekoľkých krokoch vybudovať základný miestny systém domácej automatizácie. Budeme používať Raspberry Pi, ktoré bude fungovať ako centrálne zariadenie WiFi. Zatiaľ čo pre koncové uzly použijeme kriket IOT na výrobu batérie

SYSTÉM ODVODŇOVANIA AQUARIUM NAHORU VYPNUTÝ SYSTÉM: 6 krokov

SYSTÉM ODVODŇOVANIA AQUARIUM: Systém odparovania znižuje množstvo vody v akváriu a ak zostane nekompenzovaný, povedie k zmenám v chémii zostávajúcej vody. Takéto zmeny budú mať negatívny vplyv na formy života v akváriu. Preto je dôležité, aby ste

Systém triedenia farieb: Systém založený na Arduine s dvoma pásmi: 8 krokov

Systém triedenia farieb: Systém založený na Arduino s dvoma pásmi: Doprava a/alebo balenie výrobkov a predmetov v priemyselnej oblasti sa vykonáva pomocou liniek vyrobených pomocou dopravníkových pásov. Tieto pásy pomáhajú presúvať položku z jedného bodu do druhého so špecifickou rýchlosťou. Niektoré úlohy spracovania alebo identifikácie môžu byť

Automatický systém na analýzu objemu inteligentný systém: 4 kroky

Inteligentný systém automatickej analýzy objemu: Cieľom je vytvoriť prototyp, ktorý dokáže analyzovať a identifikovať dva rôzne tvary a zobraziť jeho objem. Tu sme sa rozhodli ísť s kockou a valcom ako s dvoma rôznymi tvarmi. Dokáže sám detegovať tvary, analyzovať a vypočítať objem. Práca

Ako správne pripojiť a nastaviť mini HiFi policový systém (zvukový systém): 8 krokov (s obrázkami)

Ako správne pripojiť a nastaviť mini HiFi policový systém (zvukový systém): Som človek, ktorého baví učiť sa o elektrotechnike. Som stredná škola v Ann Richards School for Young Women Leaders. Robím to podľa pokynov, aby som pomohol každému, kto si chce vychutnať svoju hudbu z Mini LG HiFi Shelf Syste