Obsah:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:57.

- Naposledy zmenené 2025-01-23 15:05.

Pripojte svoju vývojovú dosku Mojo k externým vstupom pomocou tohto štítu.

Čo je vývojová rada Mojo?

Vývojová doska Mojo je vývojová doska založená na Xilinx spartan 3 FPGA. Dosku vyrobila spoločnosť Alchitry. FPGA sú veľmi užitočné tam, kde je potrebné vykonať viac procesov súčasne.

Čo budeš potrebovať?

Zásoby

Vývojová doska Mojo

Gerberov súbor

8 x 15 kOhm odpory (voliteľné*)

Rezistory 4 x 470 ohmov

Rezistory 4 x 560 ohmov

4 x CC sedemsegmentové displeje

LED diódy 4 x 3 mm

4 x hmatové prepínače SPDT

1 x 4 -polohový prepínač DIP na povrchovú montáž

Hlavičky 2 x 25 x 2 alebo 4 x 25

1x kolíková hlava 2 x 5 pinov

Spájkovačka

Spájka

Flux

*(ak sú tieto odpory vynechané, pre príslušné piny musí byť povolené vnútorné sťahovanie/sťahovanie)

Krok 1: Nahrajte Gerbera na výrobcu PCB podľa vášho výberu

Pre svoje dosky som si objednal z JLC PCB.

Jedinou zmenou, ktorú som urobil, bola farba, ktorú som chcel zladiť s čiernou Mojo.

Krok 2: Zostavenie dosky

Pri spájkovaní je vždy užitočné najskôr spájkovať najnižšie časti, takže začať s odpormi je dobrý nápad.

R5, R6, R7, R8, R9, R10, R11 a R12 sú odpory s odporom 15 kOhm, ktoré sa používajú na stiahnutie spínačov (ak používate vnútorné vytiahnutie/rozbalenie, toto ignorujte).

R1, R2, R3, R4 sú odpory 560 ohmov, ktoré sú zodpovedné za obmedzenie prúdu prostredníctvom 7 -segmentového displeja.

R13, R14, R15, R16 sú odpory 470 ohmov, ktoré sú zodpovedné za obmedzenie prúdu cez 4 LED diódy.

Ďalej spájkujte prepínač DIP, hmatové prepínače, diódy LED, sedemsegmentové displeje a konektor záhlavia skrinky v uvedenom poradí.

Teraz umiestnite 25 do 2 (alebo 2 25 do 1) do mojo, aby ste zarovnali kolíky. Zarovnajte štít s kolíkmi a spájkujte ho na mieste.

Krok 3: Nastavenie softvéru

Pokiaľ ide o softvér odkazujúci na webovú stránku Alchitry, dá vám vedieť, čo potrebujete na spustenie a inštaláciu Xilinx ISE. Avšak zmena súboru.ucf, aby vedel, aké piny sú spojené s tým, čo je dôležité pre spustenie programu.

Tu je súbor.ucf, ktorý používam so štítom:

KONFIGURÁCIA VCCAUX = 3,3;

NET "clk" TNM_NET = clk; TIMESPEC TS_clk = OBDOBIE „clk“50 MHz VYSOKÉ 50%; ČISTÝ "clk" LOC = P56 | IOSTANDARD = LVTTL; NET "rst_n" LOC = P38 | IOSTANDARD = LVTTL; NET "cclk" LOC = P70 | IOSTANDARD = LVTTL; NET "spi_mosi" LOC = P44 | IOSTANDARD = LVTTL; NET "spi_miso" LOC = P45 | IOSTANDARD = LVTTL; NET "spi_ss" LOC = P48 | IOSTANDARD = LVTTL; NET "spi_sck" LOC = P43 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P46 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P61 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P62 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P65 | IOSTANDARD = LVTTL; NET "avr_tx" LOC = P55 | IOSTANDARD = LVTTL; NET "avr_rx" LOC = P59 | IOSTANDARD = LVTTL; NET "avr_rx_busy" LOC = P39 | IOSTANDARD = LVTTL; NET "Q [0]" LOC = P26 | IOSTANDARD = LVTTL; ČISTÝ "Q [1]" LOC = P23 | IOSTANDARD = LVTTL; ČISTÝ "Q [2]" LOC = P21 | IOSTANDARD = LVTTL; ČISTÝ "Q [3]" LOC = P16 | IOSTANDARD = LVTTL; NET "S [0]" LOC = P7 | IOSTANDARD = LVTTL; NET "S [1]" LOC = P9 | IOSTANDARD = LVTTL; NET "S [2]" LOC = P11 | IOSTANDARD = LVTTL; NET "S [3]" LOC = P14 | IOSTANDARD = LVTTL; NET "pb [1]" LOC = P30 | IOSTANDARD = LVTTL; NET "pb [2]" LOC = P27 | IOSTANDARD = LVTTL; NET "pb [3]" LOC = P24 | IOSTANDARD = LVTTL; NET "pb [4]" LOC = P22 | IOSTANDARD = LVTTL; NET "sevsega [0]" LOC = P57 | IOSTANDARD = LVTTL; NET "sevsegb [0]" LOC = P58 | IOSTANDARD = LVTTL; NET "sevsegc [0]" LOC = P66 | IOSTANDARD = LVTTL; NET "sevsegd [0]" LOC = P67 | IOSTANDARD = LVTTL; NET "sevsege [0]" LOC = P74 | IOSTANDARD = LVTTL; NET "sevsegf [0]" LOC = P75 | IOSTANDARD = LVTTL; NET "sevsegg [0]" LOC = P78 | IOSTANDARD = LVTTL; NET "sevsegdp [0]" LOC = P80 | IOSTANDARD = LVTTL; NET "sevsega [1]" LOC = P82 | IOSTANDARD = LVTTL; NET "sevsegb [1]" LOC = P83 | IOSTANDARD = LVTTL; NET "sevsegc [1]" LOC = P84 | IOSTANDARD = LVTTL; NET "sevsegd [1]" LOC = P85 | IOSTANDARD = LVTTL; NET "sevsege [1]" LOC = P87 | IOSTANDARD = LVTTL; NET "sevsegf [1]" LOC = P88 | IOSTANDARD = LVTTL; NET "sevsegg [1]" LOC = P92 | IOSTANDARD = LVTTL; NET "sevsegdp [1]" LOC = P94 | IOSTANDARD = LVTTL; NET "sevsega [2]" LOC = P97 | IOSTANDARD = LVTTL; NET "sevsegb [2]" LOC = P98 | IOSTANDARD = LVTTL; NET "sevsegc [2]" LOC = P99 | IOSTANDARD = LVTTL; NET "sevsegd [2]" LOC = P100 | IOSTANDARD = LVTTL; NET "sevsege [2]" LOC = P101 | IOSTANDARD = LVTTL; NET "sevsegf [2]" LOC = P102 | IOSTANDARD = LVTTL; NET "sevsegg [2]" LOC = P104 | IOSTANDARD = LVTTL; NET "sevsegdp [2]" LOC = P111 | IOSTANDARD = LVTTL; NET "sevsega [3]" LOC = P114 | IOSTANDARD = LVTTL; NET "sevsegb [3]" LOC = P115 | IOSTANDARD = LVTTL; NET "sevsegc [3]" LOC = P116 | IOSTANDARD = LVTTL; NET "sevsegd [3]" LOC = P117 | IOSTANDARD = LVTTL; NET "sevsege [3]" LOC = P118 | IOSTANDARD = LVTTL; NET "sevsegf [3]" LOC = P119 | IOSTANDARD = LVTTL; NET "sevsegg [3]" LOC = P1120 | IOSTANDARD = LVTTL; NET "sevsegdp [3]" LOC = P121 | IOSTANDARD = LVTTL;

Pamätajte si, že ak ste nenainštalovali pulldown rezistory na úpravu pinov v.ucf pomocou

| VYŤAHOVANÉ; o

| VYTIAHNI;

Ak chcete blok použiť na čokoľvek, pripojenia sú nasledujúce. Vľavo je číslo PIN bloku a vpravo číslo mojo PIN, ktoré by ste mali priradiť vo svojom súbore.ucf:

kolík 1 = 29

kolík 2 = 51

kolík 3 = 32

kolík 4 = 41

kolík 5 = 34

kolík 6 = 35

kolík 7 = 40

kolík 8 = 33

kolík 9 = GND

kolík 10 = +V

Odporúča:

Vokálny GOBO - Štít tlmenia zvuku - Vokálna kabína - Vokálny box - Reflexný filter - Vokálny štít: 11 krokov

Vocal GOBO - Shield Dampener Shield - Vocal Booth - Vocal Box - Reflexný filter - Vocalshield: Začal som nahrávať viac vokálov vo svojom domácom štúdiu a chcel som získať lepší zvuk a po nejakom výskume som zistil, čo je " GOBO " bol. Videl som tieto veci tlmiace zvuk, ale poriadne som si neuvedomil, čo urobili. Teraz áno. Našiel som y

Zachytávanie videa pomocou dosky ESP32-CAM: 4 kroky

Zachytávanie videa pomocou dosky ESP32-CAM: Pozrite sa na veľmi zaujímavé úložisko GitHub, ktoré umožňuje nahrávanie videa na dosku ESP32-CAM. Video nie je nič iné ako séria starostlivo načasovaných obrázkov a na tom je založená aj táto skica. Tím tiež pridal funkciu FTP do

9 dolárový streamovač videa RTSP pomocou dosky ESP32-CAM: 3 kroky

Streamer videa RTSP za 9 dolárov pomocou dosky ESP32-CAM: Tento príspevok vám ukáže, ako môžete vytvoriť zariadenie na streamovanie videa za 9 dolárov, ktoré používa RTSP a dosku ESP32-CAM. Skicu je možné nakonfigurovať na pripojenie k existujúcej sieti WiFi alebo môže tiež vytvoriť vlastný prístupový bod, ku ktorému sa môžete pripojiť v

Viacnásobný port USB bez akejkoľvek dosky plošných spojov: 4 kroky

Viacnásobný port USB bez akejkoľvek dosky plošných spojov: Toto je môj druhý návod a tu sa s vami podelím o projekt, v ktorom môžete vytvoriť viac portov USB na použitie vo svojom počítači, pretože keď pracujete z domu, máte veľký problém s používaním mnohých zariadení, pretože väčšina zariadení teraz h

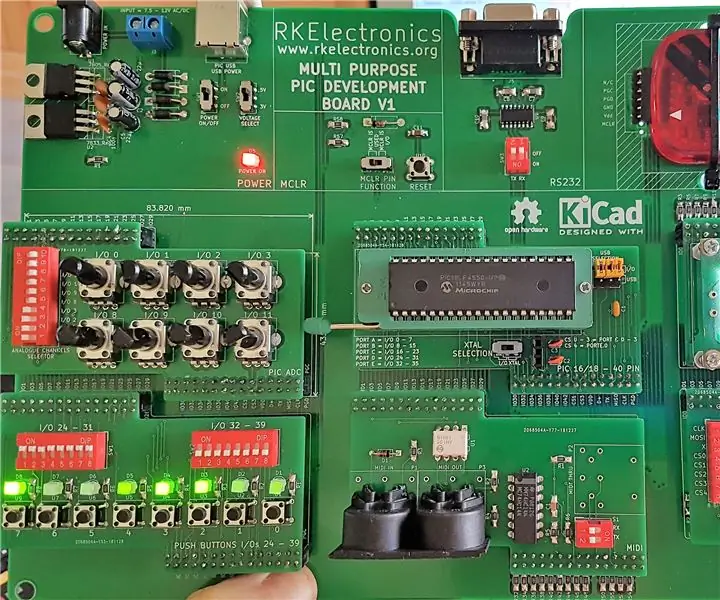

Systém vývojovej dosky mikrokontroléra PIC: 3 kroky

Systém vývojovej rady mikrokontroléra PIC: Tento projekt je určený na návrh a použitie vývojového nástroja PIC, ktorý je flexibilný, aby vyhovoval širokému spektru elektronických projektov založených na PIC. Vývoj projektov mikrokontrolérov je často jednoduchšie pomocou vývojových nástrojov; ktoré umožňujú užívateľovi