Obsah:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:57.

- Naposledy zmenené 2025-01-23 15:05.

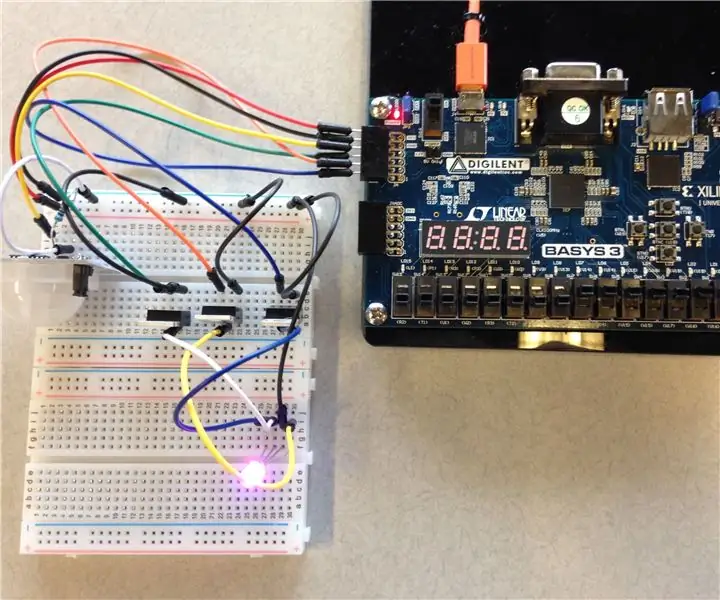

Cieľom tohto projektu bolo vytvoriť niečo, čo by komunitám ušetrilo energiu a finančné zdroje. Pohybové pouličné svetlá by urobili obe tieto veci. V celom národe sa stráca energia na pouličné osvetlenie osvetľujúce ulice, ktoré sú prázdne. Náš systém pouličného osvetlenia zaisťuje, že sa svetlá rozsvietia iba vtedy, keď je to potrebné, čo ušetrí komunitám nespočetné množstvo dolárov. Systém pomocou senzorov pohybu zapína svetlá iba vtedy, ak sú prítomné autá. Aj kvôli bezpečnosti chodcov sme implementovali tlačidlo potlačenia, ktoré rozsvieti všetky svetlá na ulici. Nasledujúce kroky vás prevedú tým, ako sme navrhli a postavili náš zmenšený model projektu pomocou dosky Vivado a Basys 3.

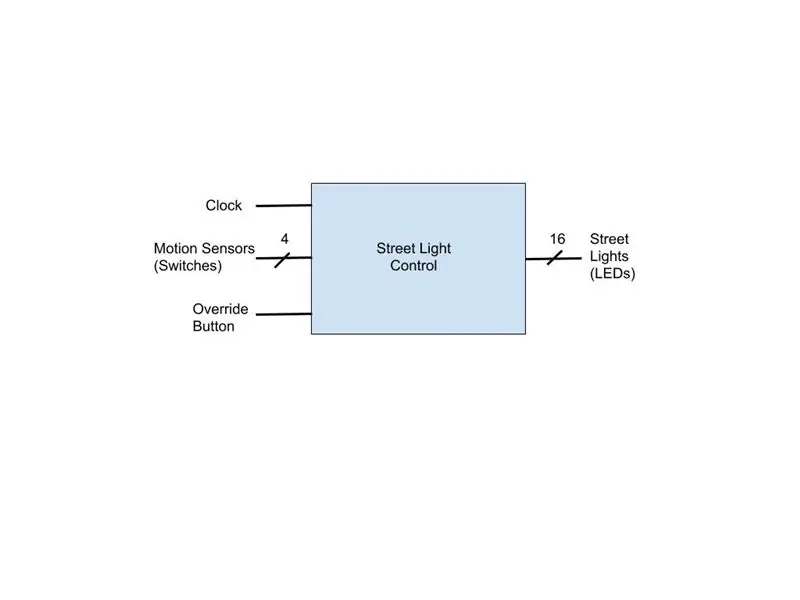

Krok 1: Systémová čierna skrinka

Tento projekt sme začali nakreslením jednoduchého diagramu čiernej skrinky. Schéma čiernej skrinky jednoducho ukazuje vstupy a výstupy, ktoré náš systém vyžaduje na dokončenie všetkých potrebných procesov. Snažili sme sa, aby bol náš dizajn čo najjednoduchší a najzákladnejší. Naše tri systémové vstupy obsahovali zbernicu pohybových senzorov (4 pre náš zmenšený model), tlačidlo pre potlačenie chodca a hodinový vstup. Na druhej strane je naším jediným výstupom zbernica LED svetiel predstavujúcich naše pouličné osvetlenie. Pre tento model sme použili scenár 16 pouličných svetiel jednoducho preto, že to je maximálny počet vstavaných LED výstupov na doske Basys 3. Nakoniec sme pomocou tohto diagramu dokázali vytvoriť náš projekt, zdrojové a obmedzovacie súbory Vivado s vhodnými vstupmi a výstupmi.

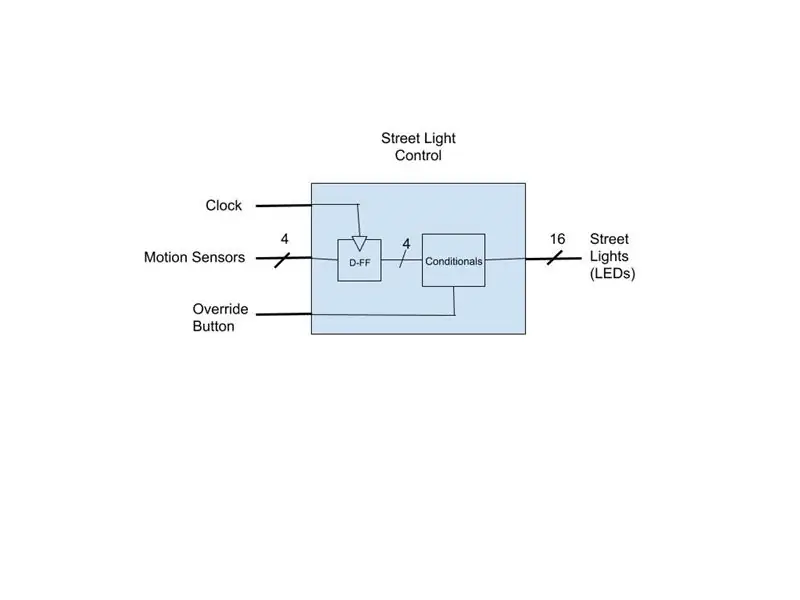

Krok 2: Komponenty

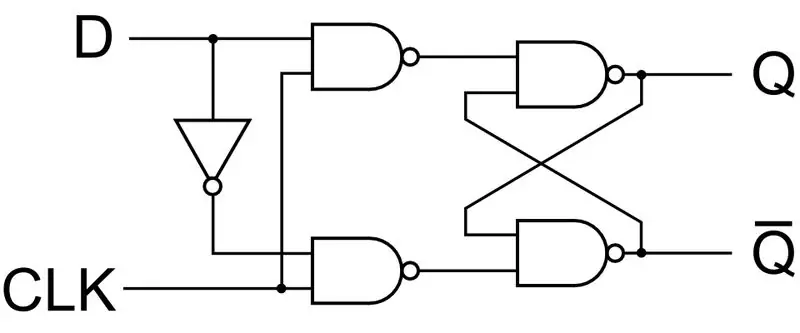

V tomto kroku sa ponoríme hlbšie do skúmania komponentov, ktoré tvoria náš diagram čiernej skrinky. Našou prvou súčasťou je zdrojový súbor VHDL obsahujúci D žabky. Žabky D jednoducho odoberajú akýkoľvek signál, ktorý im vstupuje zo senzorov na stúpajúcej hrane hodín, a zachytávajú tieto údaje až do ďalšej stúpajúcej hrany. Vďaka tomu naše citlivé snímače pohybu nespôsobujú „blikanie“LED diód výstupu. Na vstupný signál tlačidla sme tiež vložili jeden klopný obvod D, aby diódy LED svietili asi 5-7 sekúnd po stlačení tlačidla. Tiež sme to spustili cez rozdeľovač hodín.

entita clk_div2 je port (clk: in std_logic; sclk: out std_logic); koniec clk_div2;

architektúra my_clk_div z clk_div2 je

konštanta max_count: celé číslo: = (300000000); signál tmp_clk: std_logic: = '0'; začať my_div: process (clk, tmp_clk) premenná div_cnt: integer: = 0; begin if (rise_edge (clk)) then if (div_cnt = MAX_COUNT) then tmp_clk <= not tmp_clk; div_cnt: = 0; else div_cnt: = div_cnt + 1; koniec Ak; koniec Ak; sclk <= tmp_clk; ukončiť proces my_div; koniec my_clk_div;

Našim konečným komponentom v tomto diagrame je behaviorálny zdrojový súbor VHDL obsahujúci podmienené výstupy na základe konfigurácie vstupných signálov.

Krok 3: D Žabky

Štyri žabky pripojené k vstupným signálom sú nevyhnutné pre funkčnosť nášho systému. Ako už bolo povedané, s citlivými snímačmi pohybu a tlačidlom na potlačenie, žabky používajú západky iba na výstup nášho vstupného signálu na stúpajúcu hranu hodín. Táto sekvenčná logika znamená, že naše pouličné svetlá môžu zostať zapnuté určitý čas po tom, ako sa spustia rýchlym pohybom. Kódovanie D-Flip Flop je veľmi jednoduché:

beginprocess (CLK) begin if rise_edge (CLK) then Q <= D; koniec Ak; konečný proces;

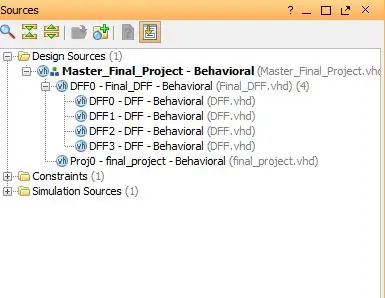

Celú vec je možné zhrnúť do jedného príkazu if. Akonáhle máme tento kus, vytvorili sme štrukturálny zdrojový súbor VHDL obsahujúci všetky štyri naše potrebné žabky:

začať DFF0: mapa portu DFF (CLK => CLK, D => D (0), Q => Q (0)); DFF1: Mapa portu DFF (CLK => CLK, D => D (1), Q => Q (1)); DFF2: Mapa portu DFF (CLK => CLK, D => D (2), Q => Q (2)); DFF3: Mapa portu DFF (CLK => CLK, D => D (3), Q => Q (3));

koniec Behaviorálne;

To pomáha udržať náš hlavný štrukturálny súbor, v ktorom spájame všetky systémové komponenty, oveľa čistší a organizovanejší.

Krok 4: Podmienky

Aby bol náš kód kompaktný a efektívny, napísali sme všetky naše podmienené výrazy do jedného prípadu. Pre náš zmenšený model sme mali 16 možných konfigurácií výstupov LED, pretože každý snímač pohybu je zodpovedný za skupinu 4 diód LED.:

prípad NMS je, keď "1111" => LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED <= "1111111111111111"; koncový prípad;

Krok 5: Obmedzenia

Aby ste správne uviedli svoje vstupy a výstupy pomocou Vivado, musíte implementovať súbor obmedzení, v ktorom budú uvedené všetky používané porty, tlačidlá, diódy LED a hodiny.

set_property PACKAGE_PIN W5 [get_ports CLK] set_property IOSTANDARD LVCMOS33 [get_ports CLK]

set_property PACKAGE_PIN U16 [get_ports {LED [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [0]}] set_property PACKAGE_PIN E19 [get_ports {LED [1]}] set_property IOSTANDARD LVCMAGE33 [get_ports U19 [get_ports {LED [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [2]}] set_property PACKAGE_PIN V19 [get_ports {LED [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [3]}] SET_property get_ports {LED [4]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [4]}] set_property PACKAGE_PIN U15 [get_ports {LED [5]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [5]}] set_property PACKAGE LED [6]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [6]}] set_property PACKAGE_PIN V14 [get_ports {LED [7]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [7]}] set_property PACKAGE_PIN V13 8]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [8]}] set_property PACKAGE_PIN V3 [get_ports {LED [9]}] set_property IO STANDARD LVCMOS33 [get_ports {LED [9]}] set_property PACKAGE_PIN W3 [get_ports {LED [10]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [10]}] set_property PACKAGE_PIN U3 [get_ports {LED [11]} [get_ports {LED [11]}] set_property PACKAGE_PIN P3 [get_ports {LED [12]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [12]}] set_property PACKAGE_PIN N3 [get_ports {LED [13]}] set_property IOSTAND {LED [13]}] set_property PACKAGE_PIN P1 [get_ports {LED [14]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [14]}] set_property PACKAGE_PIN L1 [get_ports {LED [15]}] set_property IOSTANDARD LVCM [15]}]

set_property PACKAGE_PIN U18 [get_ports BTN] set_property IOSTANDARD LVCMOS33 [get_ports BTN]

vlastnosť_sady PACKAGE_PIN A14 [get_ports {MS [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [0]}] set_property PACKAGE_PIN A16 [get_ports {MS [1]}] set_property IOSTANDARD LVCMAGE33 [1_ports] B15 [get_ports {MS [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [2]}] set_property PACKAGE_PIN B16 [get_ports {MS [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [3]}]

Krok 6: Hlavný zdrojový súbor

V tomto hlavnom súbore spájame všetky vyššie spomenuté zdrojové súbory komponentov. Tento súbor funguje ako štrukturálny kód spájajúci rôzne komponenty.

entita Master_Final_Project je port (BTN: v STD_LOGIC; CLK: v STD_LOGIC; MS: v STD_LOGIC_VECTOR (3 až 0); LED: nesvieti STD_LOGIC_VECTOR (15 až 0)); koniec Master_Final_Project;

architektúra Správanie Master_Final_Project je

komponent final_project je Port (--CLK: v STD_LOGIC; NMS: v STD_LOGIC_VECTOR (3 až 0); BTN: v STD_LOGIC; --sw: v STD_LOGIC_Vector (1 až 0); LED: mimo STD_LOGIC_VECTOR (15 až 0)); koncová zložka;

komponent Final_DFF je

Port (CLK: v STD_LOGIC; D: v STD_LOGIC_Vector (3 až 0); Q: von STD_LOGIC_Vector (3 až 0)); koncová zložka;

signál DFF02proj30: STD_LOGIC;

signál DFF12proj74: STD_LOGIC; signál DFF22proj118: STD_LOGIC; signál DFF32proj1512: STD_LOGIC;

začať

DFF0: Mapa portov Final_DFF (CLK => CLK, D (0) => MS (0), D (1) => MS (1), D (2) => MS (2), D (3) => MS (3), Q (0) => DFF02proj30, Q (1) => DFF12proj74, Q (2) => DFF22proj118, Q (3) => DFF32proj1512); Proj0: mapa portov final_project (NMS (0) => DFF02proj30, NMS (1) => DFF12proj74, NMS (2) => DFF22proj118, NMS (3) => DFF32proj1512, BTN => BTN, LED => LED); koniec Behaviorálne;

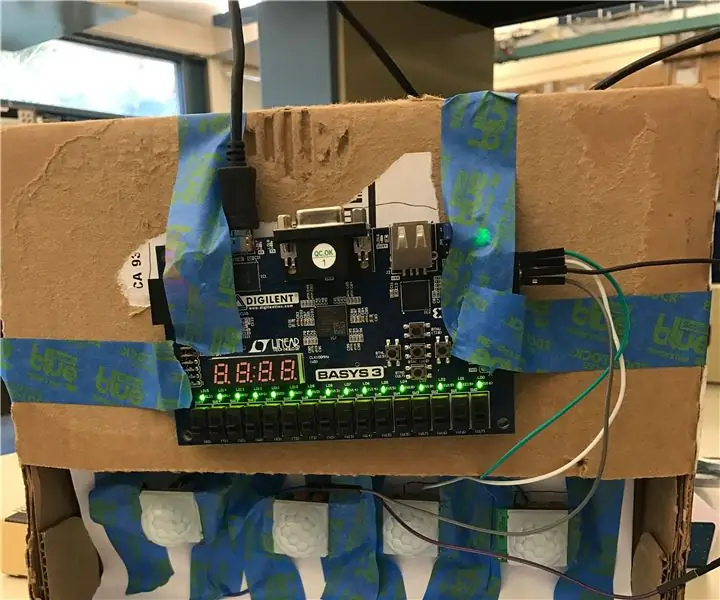

Krok 7: Zostavenie

Hardvérová zostava pre tento projekt je minimálna. Jediné požadované kusy sú nasledujúce:

1. základňa 3 doska (1)

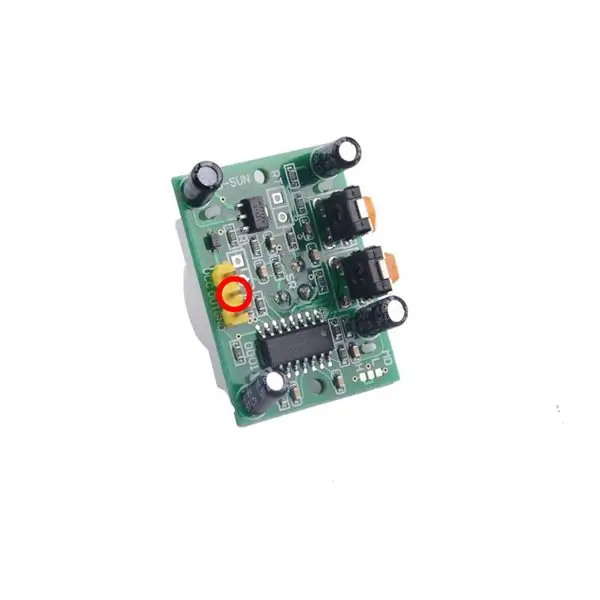

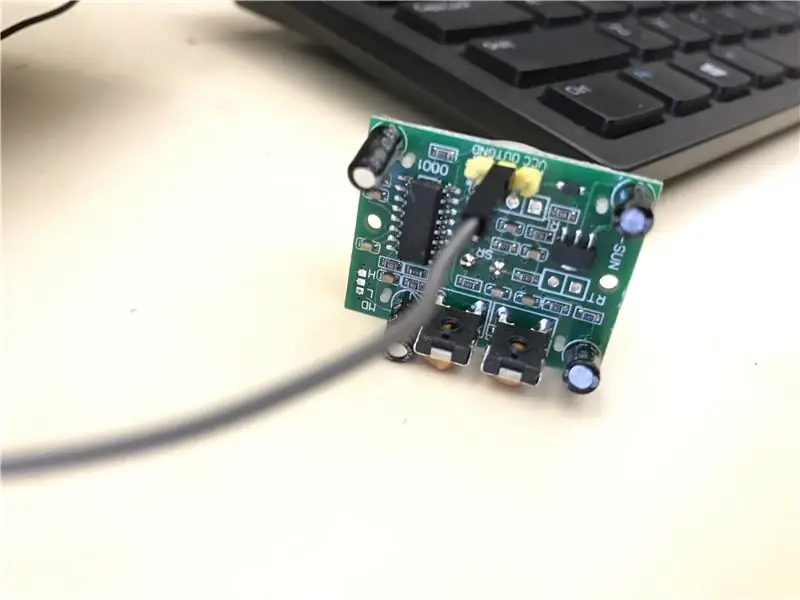

2. Lacné snímače pohybu, ktoré nájdete na amazone tu. (4)

3. Vedenie muža a ženy (4)

Zhromaždenie:

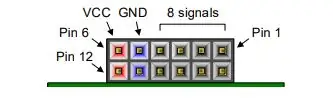

1. Pripojte 4 mužské vodiče k portom JB záhlavia PMod 1-4 (pozri obrázok).

2. Pripojte vnútorné konce k výstupnému kolíku snímača pohybu.

Krok 8: Načítanie programu

Teraz sme pripravení načítať hlavný zdrojový súbor VHDL na dosku Basys 3. Uistite sa, že spustíte syntézu, implementáciu a vygenerujete kontrolu bitového toku pre prípadné chyby. Ak všetky fungujú úspešne, otvorte správcu hardvéru a naprogramujte zariadenie Basys 3. Váš projekt je teraz dokončený!

Odporúča:

Pohybové ovládanie s Raspberry Pi a LIS3DHTR, 3-osým akcelerometrom, pomocou Pythonu: 6 krokov

Ovládanie pohybu pomocou Raspberry Pi a LIS3DHTR, 3-osového akcelerometra, pomocou Pythonu: Krása nás obklopuje, ale zvyčajne to musíme poznať tak, že sa prejdeme po záhrade. Rumi Ako vzdelaná skupina, ktorou sa zdáme byť, investujeme veľkú väčšinu energie do práce pred počítačmi a mobilnými telefónmi. Preto často nechávame blaho

Pohybové svetlá: 5 krokov

Svetlá aktivované pohybom: Táto príručka vám ukáže, ako použiť FPGA na vytvorenie svetla rôznej farby spusteného snímačom pohybu, pokiaľ je v pohybe. Úrovne červenej, modrej a zelenej sú ovládané priradením hodnoty ku každej jednotlivej farbe. Tento projekt s

Ako vytvoriť automatické pouličné osvetlenie pomocou LM555 IC: 8 krokov

Ako vytvoriť automatické pouličné osvetlenie pomocou LM555 IC: Ahoj, priateľ, dnes urobím obvod automatického pouličného osvetlenia pomocou LM555 IC. Tento obvod funguje takto Keď svetlo dopadne na LDR (za deň), potom LED nebude svietiť a keď svetlo nebude svietiť na LDR, LED bude automaticky svietiť

Ako vytvoriť automatické pouličné osvetlenie: 7 krokov

Ako vytvoriť automatické pouličné osvetlenie: Ahoj, priateľ, dnes urobím obvod automatického pouličného osvetlenia. Tento obvod bude fungovať automaticky. Ranné svetlo sa automaticky zatvorí. Tento obvod pracuje s LDR. Začnime

Pohybové stroje: 10 krokov (s obrázkami)

Pohybové stroje: Pohybové stroje poskytujú hravý úvod do pohybu, mechanizmu a robotiky. Súpravy sa skladajú z tela preglejky laserom vyrezaného a jednoduchých hromadných dielov, ako sú pomaly sa pohybujúce prevodové motory, plastové batérie a posuvné spínače. Žiaci môžu experimentovať s