Obsah:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:57.

- Naposledy zmenené 2025-01-23 15:05.

Som ohromený tým, aké reakcie na tento blog dostávam. Ďakujem, chlapci, že ste navštívili môj blog a motivovali ma, aby som sa s vami podelil o svoje znalosti. Dnes predstavím návrh ďalšieho zaujímavého modulu, ktorý vidíme vo všetkých SOC - Interrupt Controller.

Navrhneme jednoduchý, ale výkonný programovateľný ovládač prerušenia. Je to úplne konfigurovateľný a parametrizovaný dizajn, ktorý je prenosný naprieč platformami. Toto som navrhol po prečítaní mnohých obľúbených architektúr radičov prerušenia, ako sú NVIC, 8259a, RISC-V PLIC, Microblaze's INTC atď. Dúfam, že vám tento blog pomôže a pomôže vám porozumieť tomu, ako prerušenia zvláda procesor. pomocou ovládača prerušenia.

Krok 1: Špecifikácia

Nasledujú špecifikácie IP:

- Rozhranie AHB3-Lite.

-

Staticky konfigurovateľné parametre:

- Počet externých zdrojov prerušenia; podporuje až 63 prerušení.

- Počet úrovní priority; podporuje až 63 úrovní.

- Počet úrovní hniezdenia; podporuje až 8 úrovní vnorenia.

- Šírka autobusu; 32 alebo 64.

- Globálne a lokálne maskovateľné prerušenia.

- Dynamicky konfigurovateľná úroveň priority pre každé prerušenie.

- Dva režimy prevádzky - plne vnorený režim a režim rovnakej priority.

- Podporuje aktívne prerušenia citlivé na vysokej úrovni.

Pri návrhu sa používa mechanizmus prerušenia ruky inšpirovaný špecifikáciami RISC-V PLIC.

Preemption pre prerušenie je inšpirované 8259a

Ďalšie informácie: Microblaze INTC, NVIC

Krok 2: Prehľad PIC

Programovateľný radič prerušenia (PIC) prijíma viacnásobné prerušenia z externých periférií a zlúči ich do jedného výstupu prerušenia s jadrom cieľového procesora.

PIC je riadený prostredníctvom riadiacich a stavových registrov. Všetky registre PIC sú mapované do pamäte a sú prístupné prostredníctvom rozhrania zbernice AHB3-Lite.

Banka registrov pozostáva z konfiguračného registra, povolených registrov, čakajúcich registrov, registrov v prevádzke, prioritných registrov a registra ID, ktoré sú typické pre prerušovače.

Konfiguračný register slúži na nastavenie režimu prevádzky PIC. Môže fungovať buď v plne vnorenom režime, alebo v režime s rovnakou prioritou.

Každému prerušeniu je možné priradiť priority a individuálne ho maskovať. Podporované je aj globálne maskovanie všetkých prerušení.

Registračná banka spolupracuje s prioritným riešením a BTC (binárnym porovnávačom stromov), aby vyriešila priority čakajúcich prerušení a zodpovedajúcim spôsobom uplatnila prerušenie pre procesor. Register ID obsahuje ID čakajúceho prerušenia s najvyššou prioritou.

Krok 3: Návrh a implementácia RTL

Dizajn PIC kladie dôraz na zníženie latencie pri riešení priorít, čo je najdôležitejšia časť návrhu. Pretože dizajn rieši priority v jednom hodinovom cykle, výkon klesá s nárastom počtu zdrojov so zložitosťou Log2.

Návrh bol úspešne implementovaný a načasovanie overené až na nasledujúce frekvencie na FPGA Artix-7.

- Až 15 zdrojov: 100 MHz

- Až 63 zdrojov: 50 MHz

Latencia prerušenia pridaná samotným PIC sú 3 hodinové cykly (bez času na prepnutie kontextu procesora a času načítania prvého príkazu ISR).

Krok 4: Dôležité poznámky a priložené súbory

Dôležité poznámky:

- Ak je rozhranie AHB3-Lite nežiaduce, môžete zmeniť horný modul a použiť kostrový dizajn PIC. Poskytnutý testovací stôl je však pre IP s rozhraním AHB3-Lite.

- PIC IP v1.0 je úplne prenosný, holý RTL dizajn.

- Funkčne overené, aby fungovalo v oboch režimoch.

Priložené súbory:

- Navrhnite kódy a testovací stôl vo VHDL.

- Úplná dokumentácia IP.

Jedná sa o open-source dizajn … Neváhajte ho použiť …

V prípade akýchkoľvek otázok kedykoľvek:

Mitu Raj

Odporúča:

Ovládač bez prerušenia Murale Avec Domoticz Et Google Assistant: 4 kroky

Ovládač neprerušuje prácu s doménami a asistentom Google: Bonjour à tous, aujourd'hui nous alllons your simuler un doigt qui va allumer ou éteindre notre interrupteur murale grâce à un wemos d1 mini, une imprimante 3d (si vous n'en avez pas všetky vaše obľúbené výtlačky môžu mať jednu

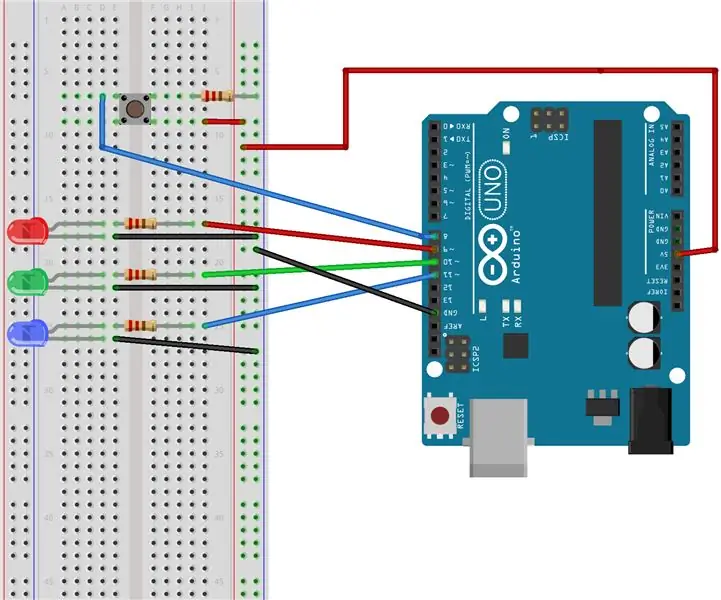

Laboratórium prerušenia (nedokončená práca): 3 kroky

Interrupts Lab (nedokončená práca): Účelom tohto laboratória je spustiť program Arduino pomocou prerušenia. Toto laboratórium nefunguje úplne správne kvôli problémom s kódovaním. Čo budete potrebovať:- 1 Arduino Uno- 1 Breadboard- 1 tlačidlo- 3 LED- odpory 220 Ohm- prepojovacie vodiče

Návrh jednoduchého štvorsmerového radiča asociatívnej vyrovnávacej pamäte vo VHDL: 4 kroky

Návrh jednoduchého štvorsmerového radiča asociatívnej vyrovnávacej pamäte vo VHDL: V mojom predchádzajúcom návode sme videli, ako navrhnúť jednoduchý radič vyrovnávacej pamäte s priamym mapovaním. Tentokrát sa posunieme o krok vpred. Navrhneme jednoduchý štvorsmerový radič asociatívnej vyrovnávacej pamäte. Výhoda? Menšia miera zmeškania, ale za cenu perfo

Návrh jednoduchého radiča vyrovnávacej pamäte vo VHDL: 4 kroky

Návrh jednoduchého ovládača vyrovnávacej pamäte vo VHDL: píšem tento návod, pretože bolo pre mňa trochu ťažké získať nejaký referenčný kód VHDL, aby som sa ho naučil a začal navrhovať radič vyrovnávacej pamäte. A tak som sám navrhol radič vyrovnávacej pamäte od začiatku a úspešne som ho otestoval na FPGA. Mám p

Návrh I2C Master vo VHDL: 5 krokov

Dizajn I2C Master vo VHDL: V tomto návode sa diskutuje o návrhu jednoduchého I2C predlohy vo VHDL. UPOZORNENIE: kliknutím na každý obrázok zobrazíte celý obrázok