Obsah:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 12:01.

- Naposledy zmenené 2025-01-23 15:06.

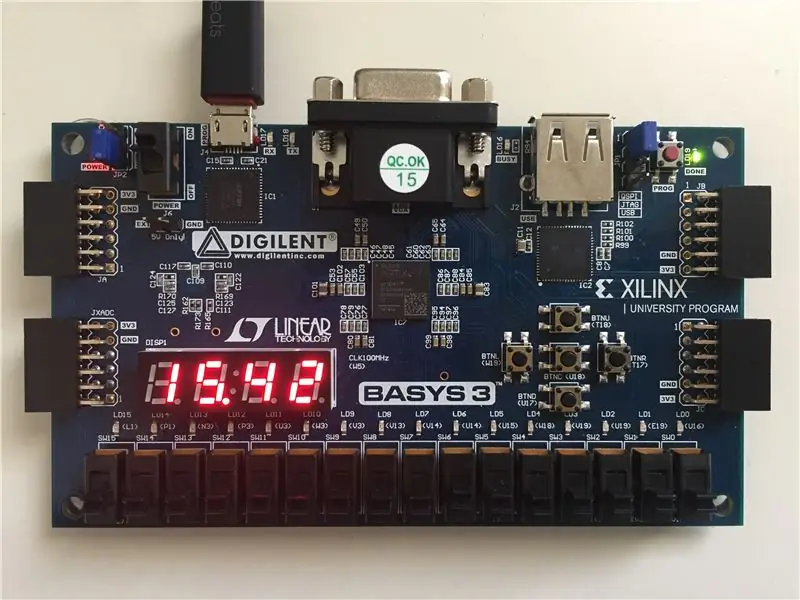

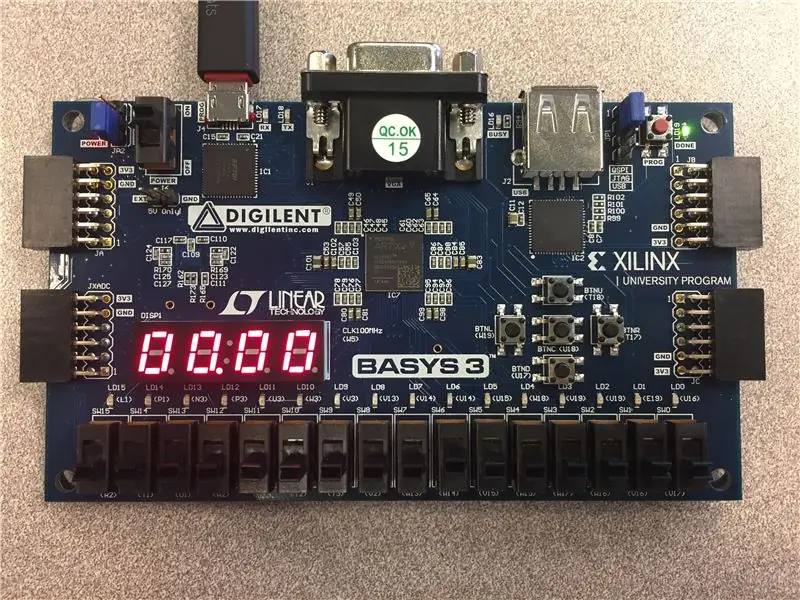

Toto je návod, ako vytvoriť stopky pomocou VHDL a dosky plošných spojov FPGA, ako je doska Basys3 Atrix-7. Stopky dokážu počítať od 00,00 sekundy do 99,99 sekundy. Používa dve tlačidlá, jedno pre tlačidlo štart/stop a druhé pre tlačidlo reset. Čísla sa zobrazujú na sedemsegmentovom displeji dosky pomocou jeho anód a katód. Na to, aby tieto stopky fungovali, sú potrebné tri rôzne súbory.

Krok 1: Hardvér/softvér

- Doska FPGA Basys3 Atrix-7

- Vivado Design Suite od Xilinx

- USB 2.0 A samec na Micro-B samec

Krok 2: Blokový diagram

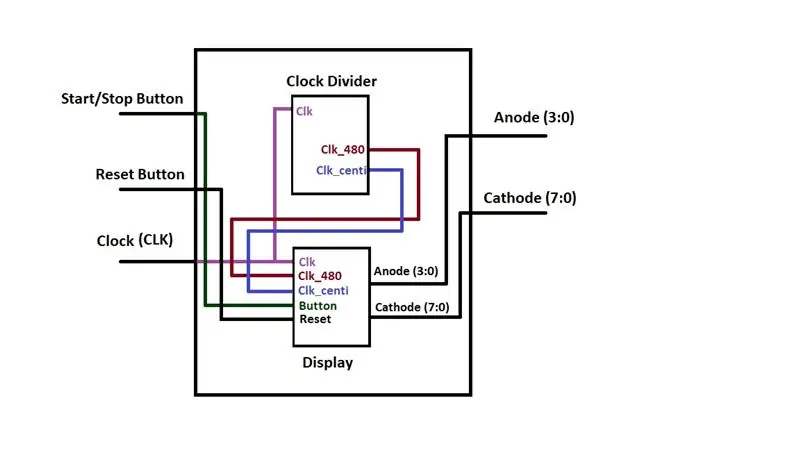

Celkové stopky majú tri vstupy a dva výstupy. Tri vstupy sú štart/stop, reset a hodiny. Štart/stop a reset sú tlačidlá a hodiny majú hodiny s frekvenciou 100 MHz. Dva výstupy sú anódy a katódy pre sedemsegmentový displej.

Prvý modul (rozdeľovač hodín) má jeden vstup a dva výstupy. Vstupom sú hodiny s frekvenciou 100 MHz a výstupmi sú dva samostatné hodiny, jeden beží na 480 Hz a druhý na 0,5 MHz.

Druhý modul (displej) má päť vstupov a dva výstupy. Vstupmi sú hodiny 100 MHz na doske, dva hodiny z modulu rozdeľovača hodín a tlačidlá štart/stop a reset. Výstupom sú anódy a katódy.

Posledný modul (modelovaný celým blokovým diagramom) má tri vstupy a dva výstupy. Toto je súbor, ktorý spája všetko. Vstupy sú 100 MHz na doske a tlačidlá štart/stop a reset. Výstupmi sú anódy a katódy, ktoré ovládajú sedemsegmentový displej. Všetky vstupy a výstupy sú fyzicky na doske konečného modulu.

Krok 3: Stavový diagram

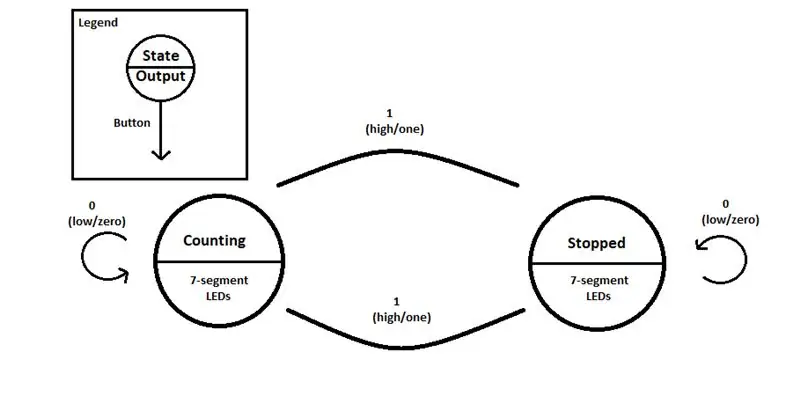

Na obrázku vyššie je znázornený stavový diagram fungovania stopiek. Stlačenie resetovacieho tlačidla nemá vplyv na stav stopiek. Ďalší stav je určený tlačidlom štart/stop. Štart/stop je pri stlačení „HIGH“, ale nie pri stlačenom tlačidle, a „LOW“, keď sa tlačidlo odrazilo späť alebo bolo pridržané po tom, čo bolo na chvíľu „HIGH“.

Ak stopky počítajú a tlačidlo štart/stop prejde na „VYSOKÉ“, počítanie sa zastaví. Ak sa stopky zastavia a tlačidlo štart/stop prejde na „VYSOKÉ“, začne počítanie znova. Pokiaľ je v oboch stavoch tlačidlo štart/stop „NÍZKE“, potom zostane v stave, v ktorom sa práve nachádza.

Krok 4: Modul oddeľovača hodín

Modul deliča hodín má jeden vstup, hodiny na doske 100 MHz a dva výstupy, hodiny 480 Hz a 0,5 MHz. Hodiny 480 Hz sa používajú na udržanie všetkých LED diód na sedemsegmentovom displeji súčasne „zapnutých“rýchlym prepínaním medzi štyrmi. Hodiny 0,5 MHz sa používajú na to, aby stopky skutočne počítali o centi-sekundy.

Krok 5: Zobrazovací modul

Tento zobrazovací modul má päť vstupov, hodiny na doske 100 MHz, dva hodiny z hodinového modulu a tlačidlá štart/stop a reset a dva výstupy, anódy a katódy. Tento modul má tiež „logiku“, ako stopky počítajú, a obsahuje automat konečného stavu.

Krok 6: Väzobný modul

Tento posledný modul spája ostatné dva moduly. Má tri vstupy, hodiny na doske 100 MHz a tlačidlá štart/stop a reset a dva výstupy, anódy a katódy. Hodiny 100 MHz prechádzajú na modul rozdeľovača hodín a modul displeja a tlačidlá štart/stop a reset smerujú k modulu displeja. Výstupy modulu rozdeľovača hodín (480 Hz a 0,5 MHz) smerujú k dvom hodinovým vstupom zobrazovacieho modulu. Výstupy zobrazovacieho modulu (anódy a katódy) idú na výstupy konečného modulu.

Krok 7: Obmedzenia

Dva vstupy môžu byť akékoľvek tlačidlá na doske FPGA Basys3 Atrix-7 FPGA a výstupmi budú štyri anódy a osem katód (pretože chcete tiež desatinnú čiarku medzi sekundami a milisekundami) pre sedemsegmentový displej.

Krok 8: Hotovo

Nahrajte program na svoju dosku Basys3 Atrix-7 FPGA a stopky spustíte stlačením tlačidla štart/stop!

Odporúča:

Ako vytvoriť stopky pomocou Arduina: 8 krokov (s obrázkami)

Ako vytvoriť stopky pomocou Arduina: Jedná sa o veľmi jednoduché Arduino 16*2 LCD stopky s displejom ……….. Ak sa vám páči tento návod, prihláste sa na odber môjho kanála https://www.youtube.com /ZenoModiff

Základné stopky používajúce dosku VHDL a Basys3: 9 krokov

Základné stopky pomocou dosky VHDL a Basys3: Vitajte v návode, ako zostaviť stopky pomocou základnej dosky VHDL a Basys 3. Sme radi, že sa s vami môžeme podeliť o náš projekt! Toto bol konečný projekt pre kurz CPE 133 (digitálny dizajn) na Cal Poly, SLO na jeseň 2016. Projekt, ktorý sme vytvorili

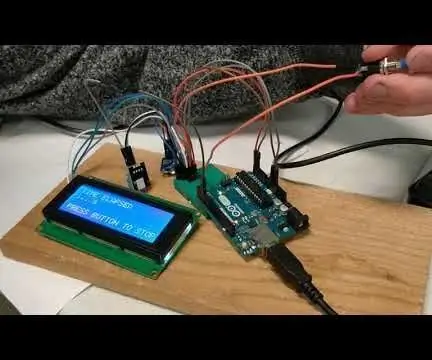

Jednoduché hodiny / stopky Arduino: 6 krokov (s obrázkami)

Jednoduché hodiny / stopky Arduino: Tieto " inštrukcie " v niekoľkých jednoduchých krokoch vám ukáže a naučí vás vyrobiť jednoduché hodiny Arduino Uno, ktoré zároveň slúžia ako stopky

Stopky na 30 m beh (Arduino): 6 krokov (s obrázkami)

Stopky na 30 m beh (Arduino): Tento projekt bol vytvorený na špecifický účel vo fínskom baseballe, ktorý trénuje a testuje rýchlosť mladých hráčov v behu na 30 m. Tento arduino projektck bol tiež projektom kurzu počas môjho štúdia. Projekt mal niekoľko vzostupov a pádov, ale teraz prinajmenšom funguje

Jednominútové stopky VHDL: 5 krokov

Jednominútové stopky VHDL: Toto je návod, ako vytvoriť jednominútové stopky pomocou VHDL a dosky Basys 3. Takéto zariadenie je ideálne pre hry, kde každý hráč má na svoj ťah maximálne jednu minútu. Stopky presne zobrazujú sekundy a milisekundy