Obsah:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 12:01.

- Naposledy zmenené 2025-01-23 15:06.

Toto je návod, ako vytvoriť jednominútové stopky pomocou VHDL a dosky Basys 3. Takéto zariadenie je ideálne pre hry, kde každý hráč má na svoj ťah maximálne jednu minútu. Stopky presne zobrazujú sekundy a milisekundy na sedemsegmentovom displeji, začínajúc od 0 sekúnd a 0 milisekúnd, až po 60 sekúnd a 0 milisekúnd. Používajú sa aj dve tlačidlá: stredové tlačidlo, ktoré slúži na spustenie, zastavenie a pokračovanie časovača, a pravé tlačidlo slúžiace na reštartovanie časovača. Keď sa zariadenie porovná bok po boku so vstavanými stopkami inteligentného telefónu, je zrejmá presnosť hodín.

Krok 1: Získajte hardvér/softvér

1. Basys 3 Artix-7 FPGA Trainer Board od spoločnosti Digilent s káblom Micro-USB na USB

2. Vivado 2016.2 Design Suite od spoločnosti Xilinx

Krok 2: Blokový diagram

Tento obvod je konštruovaný behaviorálne a používa vstavané komponenty Xilinx, ale môže byť tiež popísaný štrukturálne, ako ukazuje všeobecný štruktúrny diagram vyššie. Z diagramu je zrejmé, že obvod je poháňaný dvoma frekvenčnými deličmi. Jeden z frekvenčných deličov beží na 1 centisekundu a poháňa katódové počítadlo, ktoré sa používajú ako čísla zobrazené na sedemsegmentovom displeji. Druhý delič frekvencie beží na 240 Hz a slúži na pohon anódového počítadla, ktoré sa otáča anódami, aby sa všetky čísla správne zobrazovali na sedemsegmentovom displeji. Kodér preberá katódovú logiku z katódového počítadla a anódovú logiku z anódového počítadla a kóduje ho na výstupnú katódu a anódu, ktoré spúšťajú sedemsegmentový displej. Funkciou tohto kodéra je, aby sa výstup katódy menil vždy, keď sa zmení výstup anódy. Katódový výstup nemožno spustiť nezávisle od počítadla, pretože anódy sa musia otáčať cez 4 oddelené číslice.

Krok 3: Modul projektu

Po prvé, procesný blok pre CEN sa robí tak, že keď sa zistí stlačenie tlačidla, ENABLE sa prepne. Toto slúži ako zastavenie/spustenie katódového počítadla.

V nasledujúcom bloku procesu sú hodinové signály v centisekundách a 240 Hz nastavené tak, aby sa ich príslušné počítadlá zvýšili o 1 zakaždým, keď vnútorné hodiny 100 MHz dosiahnu stúpajúcu hranu. Akonáhle počítadlo centisekúnd dosiahne 500 000, vynuluje sa späť na 0. Medzitým sa počítadlo 240 Hz vynuluje, keď počet dosiahne 41667.

Pokiaľ je v sekcii katódy v kóde hodnota ENABLE „0“, počítanie katódy sa pozastaví. Ak počas tejto doby stlačíte tlačidlo reset, všetky počty sa vynulujú na „0000“. Medzitým, ak je ENABLE „1“, počítanie katódy bude pokračovať, kým počet katód nedosiahne 60,00, v ktorom spustí stop signál „1“. Signál zastavenia smeruje späť do procesného bloku CEN a spôsobí, že hodnota ENABLE je „0“, kým je signál zastavenia „1“, a nezmení sa, kým nestlačíte tlačidlo reset.

Nakoniec je sedemsegmentový displej nastavený tak, že 4 anódy sú správne spojené s každou z ich 8 katód, aby sa súčasne zobrazili ich príslušné číslice 0 až 9.

Krok 4: Obmedzenia

Tento súbor obmedzení spája špecifikované vstupy a výstupy z VHDL s potrebnými fyzickými časťami dosky Basys. V tomto projekte súčiastky obsahujú štyri anódy a každú z ich ôsmich katód pre sedemsegmentový displej, vnútorné hodiny 100 MHz, stredné tlačidlo a pravé tlačidlo.

Krok 5: Test

Po dokončení kódu môžete teraz programovať FPGA pomocou kábla USB. Sedemsegmentový displej by mal ukazovať 0,00. Otestujte, či tlačidlá fungujú, stlačením stredového tlačidla spustíte časovač, kým sa nedosiahne 60,00 a nezastaví sa; kedykoľvek medzi tým môžete pozastavenie pozastaviť opätovným stlačením stredného tlačidla. Akonáhle je pozastavený, môžete stlačením pravého tlačidla resetovať časovač späť na 0,00. Ak všetko funguje správne, gratulujeme, práve ste si vytvorili minútový časovač!

Odporúča:

Udržiavanie stopky jednoduchého internetového rádia: KISSIR: 13 krokov

Jednoduché webové internetové rádio: KISSIR: Niekedy musí byť iba hmatateľné. Žiadne rozhranie akéhokoľvek druhu. Len tlačidlá. Malina Pi ako prehrávač internetového rádia nie je nič nové a existuje množstvo návodov, ako vytvoriť prehrávač internetového rádia pomocou malinového pi s alebo bez

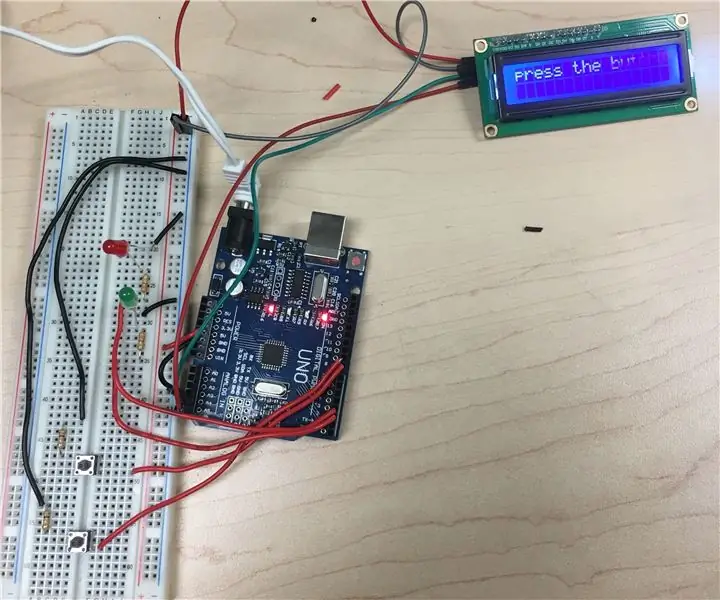

Stopky Arduino pomocou I2C LCD: 5 krokov

Stopky Arduino pomocou I2C LCD: V tomto projekte vás naučím používať LCD displej a Arduino ako interaktívne stopky. Keď je váš projekt hotový s poskytnutým kódom, mal by vyzerať ako vyššie uvedená fotografia. Prejdite na ďalší krok a zistite, kde začať

Automatické stopky: 9 krokov

Automatické stopky: Tento návod vám ukáže, ako vytvoriť automatické stopky. Pretože beh je zábava, ale niekedy nemáte pri sebe nikoho, kto by vás dokázal načasovať. Snažil som sa, aby to bolo čo najjednoduchšie, najlacnejšie a najpresnejšie. Nepotrebujete diaľkové ovládanie

Základné stopky používajúce dosku VHDL a Basys3: 9 krokov

Základné stopky pomocou dosky VHDL a Basys3: Vitajte v návode, ako zostaviť stopky pomocou základnej dosky VHDL a Basys 3. Sme radi, že sa s vami môžeme podeliť o náš projekt! Toto bol konečný projekt pre kurz CPE 133 (digitálny dizajn) na Cal Poly, SLO na jeseň 2016. Projekt, ktorý sme vytvorili

Stopky VHDL: 8 krokov (s obrázkami)

Stopky VHDL: Toto je návod, ako vytvoriť stopky pomocou VHDL a dosky plošných spojov FPGA, ako je doska Basys3 Atrix-7. Stopky dokážu počítať od 00,00 sekundy do 99,99 sekundy. Používa dve tlačidlá, jedno pre tlačidlo štart/stop a druhé pre