Obsah:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:59.

- Naposledy zmenené 2025-01-23 15:05.

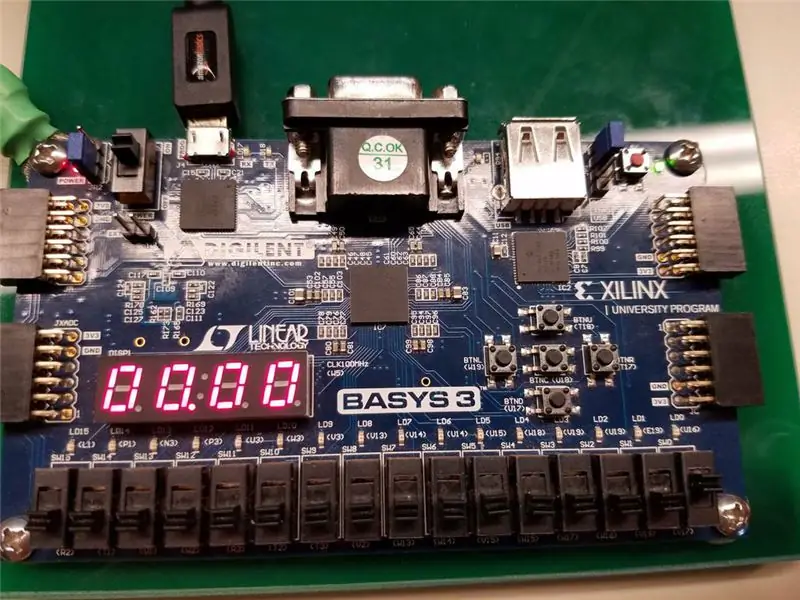

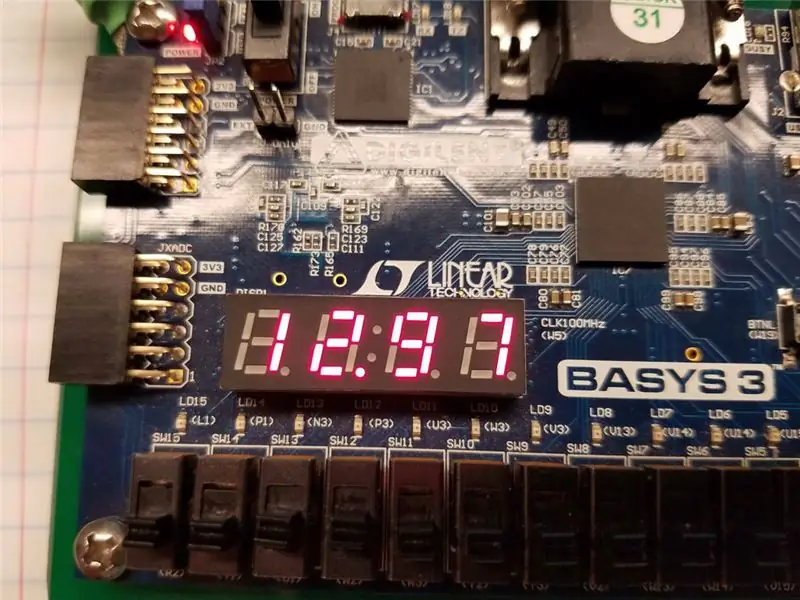

Vitajte v návode, ako vytvoriť stopky pomocou základnej dosky VHDL a Basys 3. Sme radi, že sa s vami môžeme podeliť o náš projekt! Toto bol konečný projekt pre kurz CPE 133 (Digital Design) na Cal Poly, SLO na jeseň 2016. Projekt, ktorý sme vytvorili, sú jednoduché stopky, ktoré začínajú, resetujú a pozastavujú čas. Ako vstupy sú potrebné tri tlačidlá na doske Basys3 a čas sa zobrazuje na štvormiestnom sedemsegmentovom displeji dosky. Uplynulý čas sa zobrazuje vo formáte sekundy: centisekundy. Systémové hodiny na doske používa ako vstup na sledovanie uplynutého času a vydáva čas na štyri číslice sedemsegmentového displeja.

Krok 1: Materiály

Materiály, ktoré budete potrebovať pre tento projekt:

- 1 počítač s Vivado Design Suite WebPack nainštalovaným z Xilinx (preferovaná verzia 2016.2)

- 1 doska Digilent Basys3 Xilinx Artix-7 FPGA

- 1 kábel portu USB

Krok 2: Nastavenie vstupov a výstupov

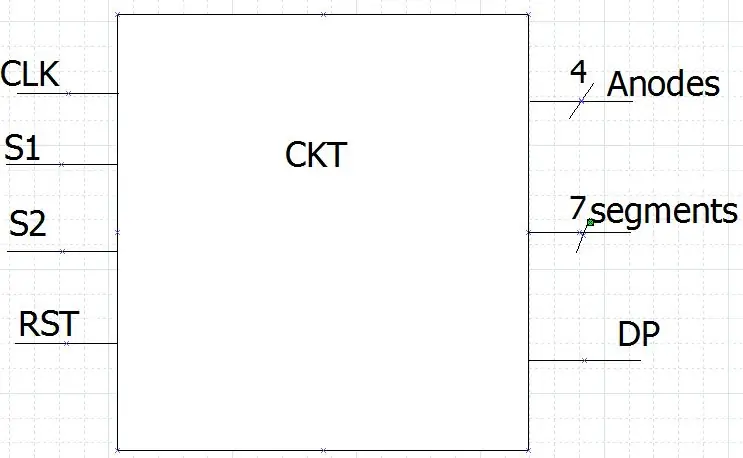

Vyššie uvedený obrázok zobrazuje blokový diagram najvyššej úrovne hlavného modulu stopiek. Stopky prijímajú vstupy „CLK“(hodiny), „S1“(tlačidlo štart), „S2“(tlačidlo pozastavenia) a „RST“(reset) a majú 4-bitový výstup „Anodes“, 7-bitový výstupný „segment“a jednobitový výstup „DP“(desatinná čiarka). Keď je vstup „S1“vysoký, stopky začnú počítať čas. Keď je hodnota „S2“nízka, stopky pozastavia čas. Keď je „RST“vysoké, stopky sa zastavia a vynulujú čas. V obvode sú štyri submoduly: rozdeľovač hodín, číselný čítač, sedemsegmentový ovládač displeja a kodér sedemsegmentového displeja. Hlavný modul stopiek spája všetky submoduly dohromady a so vstupmi a výstupmi.

Krok 3: Výroba hodín

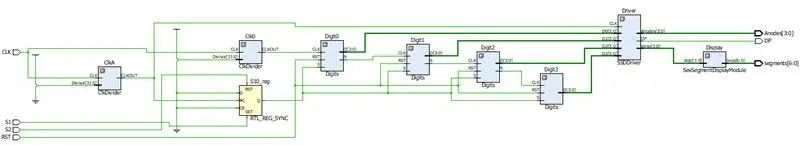

Modul deliča hodín preberá systémové hodiny a pomocou vstupu deliteľa vytvára hodiny s akoukoľvek rýchlosťou, ktorá nie je väčšia ako rýchlosť systémových hodín. Stopky používajú dva rôzne hodinové moduly, pričom jeden vytvára hodiny s frekvenciou 500 Hz a druhý vytvára hodiny s frekvenciou 100 Hz. Schéma rozdeľovača hodín je znázornená na obrázku vyššie. Hodinový delič má jednobitový vstup „CLK“a 32-bitový vstup „Divizor“a jednobitový výstup „CLKOUT“. „CLK“sú systémové hodiny a „CLKOUT“sú výsledné hodiny. Modul tiež obsahuje bránu NOT, ktorá prepína signál "CLKTOG", keď počet dosiahne hodnotu deliteľa.

Krok 4: Počítanie do desať

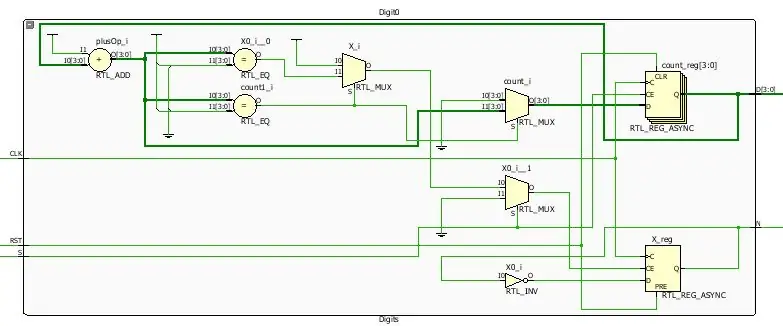

Počítadlo číslic počíta každú číslicu od 0 do 10 a vytvorí ďalšie hodiny, na ktorých bude fungovať ďalšia číslica, ktorá osciluje, keď počet dosiahne 10. Modul prijíma tri jednobitové vstupy „S“, „RST“a „CLK““a výsledkom je jednobitový výstup„ N “a 4-bitový výstup„ D “. Vstup „S“je vstup na uvoľnenie. Hodiny sa zapnú, keď je „S“vysoko, a vypne sa, keď je „S“nízko. „RST“je vstup resetovania, takže hodiny sa vynulujú, keď je „RST“vysoké. „CLK“je hodinový vstup pre počítadlo číslic. „N“je hodinový výstup, ktorý sa stane vstupným hodinami pre ďalšiu číslicu. Výstup „D“predstavuje binárnu hodnotu číslice, na ktorej sa čítač nachádza.

Krok 5: Zobrazenie čísel

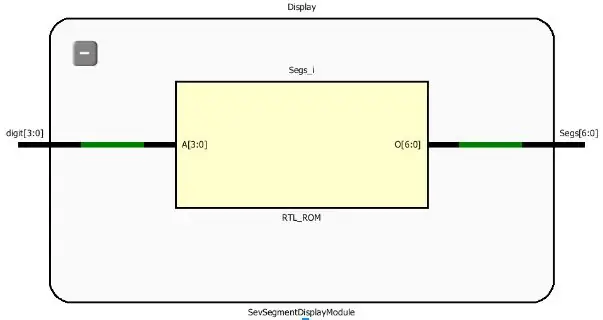

Sedemsegmentový kodér displeja zakóduje binárne číslo prijaté z modulu ovládača sedemsegmentového displeja a zmení ho na prúd bitov, ktoré budú interpretované ako hodnoty „1“alebo „0“pre každý segment displeja. Binárne číslo modul prijme ako 4-bitovú vstupnú „číslicu“a výsledkom sú 7-bitové výstupné „segmenty“. Modul pozostáva z jedného bloku procesného prípadu, ktorý priraďuje konkrétny 7-bitový tok pre každú možnú vstupnú hodnotu od 0 do 9. Každý bit v sedembitových tokoch predstavuje jeden zo siedmich segmentov číslic na displeji. Poradie segmentov v streame je „abcdefg“, pričom „0“predstavujú segmenty, ktoré sa rozsvietia pre dané číslo.

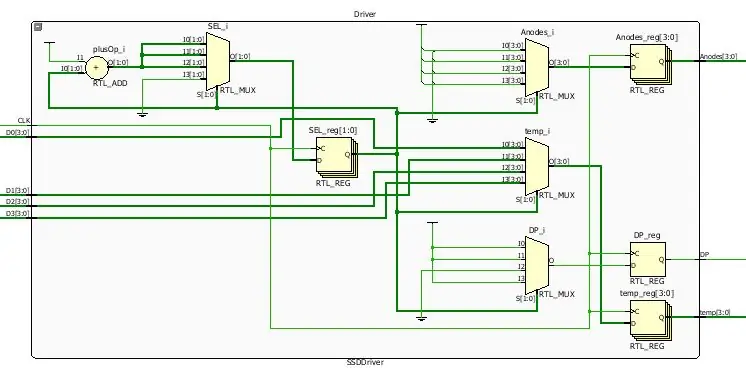

Krok 6: Ako zobraziť stopky

V module ovládača sedemsegmentového displeja sú štyri 4-bitové vstupy „D0“, „D1“, „D2“a „D3“, pričom každý predstavuje štyri číslice, ktoré sa majú zobraziť. Vstup „CLK“je hodinový vstup systému. Jednobitový výstup „DP“predstavuje desatinnú čiarku na sedemsegmentovom displeji. 4-bitový výstup „Anodes“určuje, ktorá číslica na sedemsegmentovom displeji sa zobrazí a 4-bitový výstup „temp“závisí od stavu 2-bitového riadiaceho vstupu „SEL“. Modul používa 4 multiplexory na riadiaci vstup „SEL“a tri výstupy; „Anódy“, „teplota“a „DP“.

Krok 7: Spojte to všetko dohromady

Na vytvorenie tlačidiel spustenia a pozastavenia sa používa procesný blok „ak“, ktorý beží na frekvencii 500 Hz. Potom prepojte všetky submoduly dohromady v hlavnom module stopiek deklarovaním komponentov každého jednotlivého submodulu a použitím rôznych signálov. Číslicové submoduly preberajú hodinový výstup predchádzajúceho číslicového submodulu, pričom prvý modul má hodiny 100 Hz. Výstupy „D“digitálnych submodulov sa potom stanú vstupmi „D“modulu ovládača siedmich segmentových displejov. A nakoniec „tempový“výstup modulu ovládača sedemsegmentového displeja sa stane „dočasným“vstupom modulu sedemsegmentového snímača.

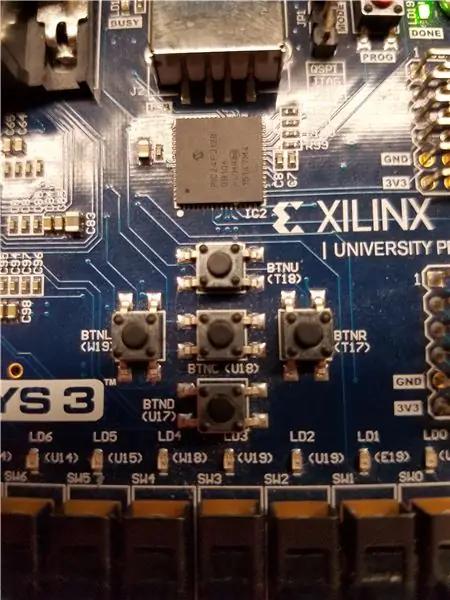

Krok 8: Obmedzenia

Na vstupy „RST“, „S1“a „S2“použite 3 tlačidlá (W19, T17 a U18). W19 je resetovacie tlačidlo, T17 je štartovacie tlačidlo (S1) a U18 je tlačidlo pozastavenia (S2). Prostredníctvom portu W5 je tiež potrebné obmedziť vstup hodinového vstupu. Nezabudnite tiež pridať tento riadok do obmedzenia hodín:

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports {CLK}]

Pripojte tiež anódy a segmenty k doske, aby sa stopky zobrazovali na sedemsegmentovom displeji, ako je vidieť v súbore obmedzení.

Krok 9: Testovanie

Zaistite, aby vaše zariadenie fungovalo, hraním sa s tromi tlačidlami: stlačením a podržaním ich v každom možnom poradí, aby ste zistili prípadné problémy s kódom.

Odporúča:

Text na reč Kliknite na ARM základne poháňanú UChip a ďalšie ARM základne poháňané SBC: 3 kroky

Prevod textu na reč Kliknite na ARMbasic Powered UChip a ďalšie ARMbasic poháňané SBC: Úvod: Dobrý deň. Volám sa Tod. Som profesionál v oblasti letectva a obrany, ktorý je tiež trochu geek. Inšpirácia: Pochádza z éry dial-up BBS, 8-bitových mikrokontrolérov, osobných počítačov Kaypro/Commodore/Tandy/TI-994A, keď R

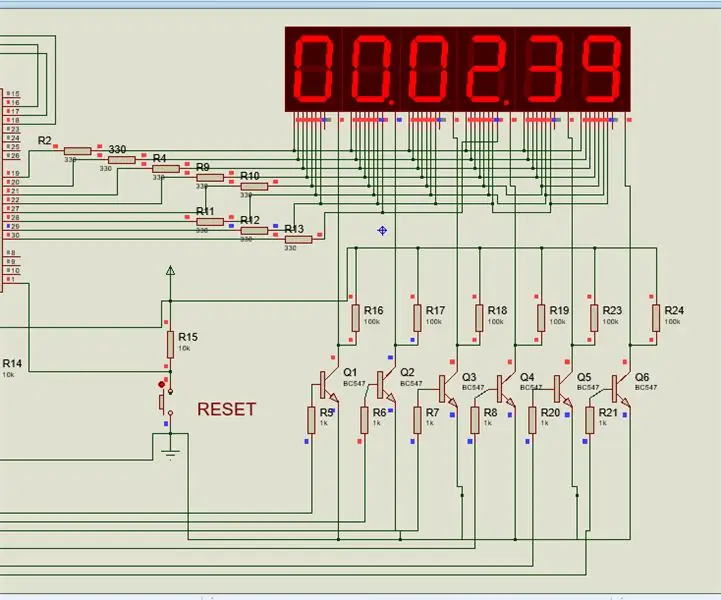

Stopky používajúce Pic18f4520 v Proteuse so 7 segmentmi: 6 krokov

Stopky používajúce Pic18f4520 v Proteuse so 7 segmentom: Práve som začal pracovať s ovládačom obrazu, jeden z mojich priateľov ma požiadal, aby som z nich vyrobil stopky. Nemám teda hardvér, ktorý by som mohol zdieľať, napísal som kód a simuloval ho v softvéri Proteus. Tu som zdieľal schému rovnakého postupu. T

Jednominútové stopky VHDL: 5 krokov

Jednominútové stopky VHDL: Toto je návod, ako vytvoriť jednominútové stopky pomocou VHDL a dosky Basys 3. Takéto zariadenie je ideálne pre hry, kde každý hráč má na svoj ťah maximálne jednu minútu. Stopky presne zobrazujú sekundy a milisekundy

Stopky VHDL: 8 krokov (s obrázkami)

Stopky VHDL: Toto je návod, ako vytvoriť stopky pomocou VHDL a dosky plošných spojov FPGA, ako je doska Basys3 Atrix-7. Stopky dokážu počítať od 00,00 sekundy do 99,99 sekundy. Používa dve tlačidlá, jedno pre tlačidlo štart/stop a druhé pre

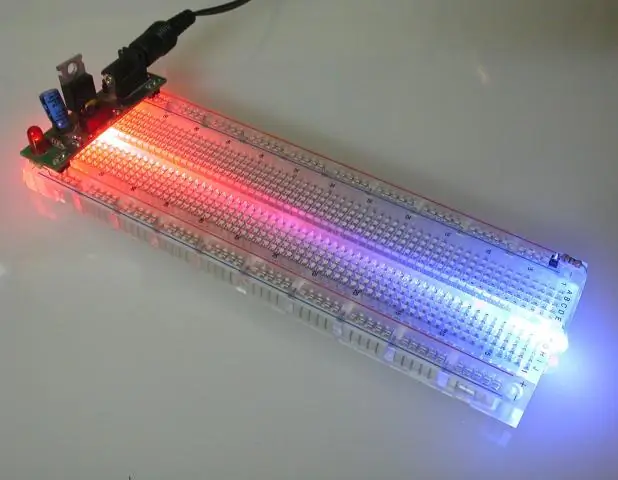

Vymažte dosku (ako pridať LED indikátor napájania na transparentnú dosku Solarbotics): 7 krokov

Vymažte si dosku (ako pridať LED indikátor napájania na priehľadnú dosku Solarbotics): Tieto priehľadné doštičky sú veľmi podobné ako všetky ostatné dosky na elektroniku, ale sú jasné! Čo teda dá človek robiť s čistým chlebíkom? Myslím, že jasnou odpoveďou je pridať LED diódy napájania