Obsah:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:57.

- Naposledy zmenené 2025-01-23 15:05.

V tomto návode popíšeme, ako implementovať 8-bitový analógovo-digitálny prevodník (ADC) do SLG46855V, ktorý dokáže snímať záťažový prúd a rozhranie s MCU cez I2C. Túto konštrukciu je možné použiť pre rôzne aplikácie na snímanie prúdu, ako sú ampérmetre, systémy detekcie porúch a palivomery.

Ďalej sme popísali potrebné kroky, aby ste pochopili, ako bolo riešenie naprogramované tak, aby vytváralo súčasný zmysel ADC. Ak však chcete získať iba výsledok programovania, stiahnite si softvér GreenPAK a zobrazte už dokončený súbor návrhu GreenPAK. Pripojte vývojovú súpravu GreenPAK k počítaču a spustite program, aby ste vytvorili súčasný zmysel ADC.

Krok 1: Architektúra ADC

ADC sa v zásade skladá z analógového komparátora a prevodníka digitálneho signálu na analógový (DAC). Komparátor sníma vstupné napätie oproti výstupnému napätiu DAC a následne kontroluje, či sa má vstupný kód DAC zvýšiť alebo znížiť, takže výstup DAC konverguje na vstupné napätie. Výsledný vstupný kód DAC sa stane digitálnym výstupným kódom ADC.

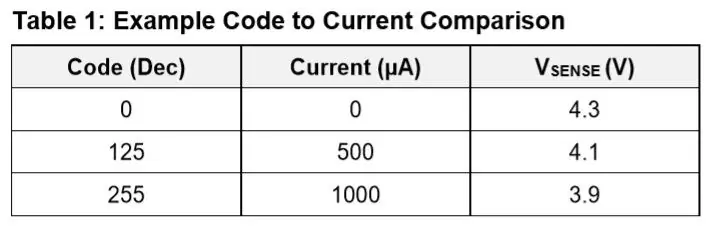

V našej implementácii vytvárame DAC pomocou siete odporov riadenej pulznou šírkovou moduláciou (PWM). Pomocou GreenPAK môžeme ľahko vytvoriť presný digitálne riadený výstup PWM. Keď je PWM filtrovaný, stáva sa naším analógovým napätím a slúži teda ako účinný DAC. Výraznou výhodou tohto prístupu je, že je ľahké nastaviť napätie, ktoré zodpovedá nulovému kódu a plnej stupnici (ekvivalentne posunuté a zosilnené) jednoduchým nastavením hodnôt odporu. Užívateľ chce napríklad v ideálnom prípade prečítať nulový kód z teplotného snímača bez prúdu (0 µA) zodpovedajúceho 4,3 V a úplného kódu pri 1000 µA zodpovedajúceho 3,9 V (tabuľka 1). To sa dá ľahko implementovať jednoduchým nastavením niekoľkých hodnôt odporu. Tým, že sa rozsah ADC zhoduje s požadovaným rozsahom snímačov, maximálne využívame rozlíšenie ADC.

Pri návrhu tejto architektúry sa zvažuje, že interná frekvencia PWM musí byť oveľa rýchlejšia ako aktualizačná frekvencia ADC, aby sa zabránilo podtlumenému správaniu jej riadiacej slučky. Minimálne by mal byť dlhší ako hodiny počítadla údajov ADC delené 256. V tomto návrhu je doba aktualizácie ADC nastavená na 1,3312 ms.

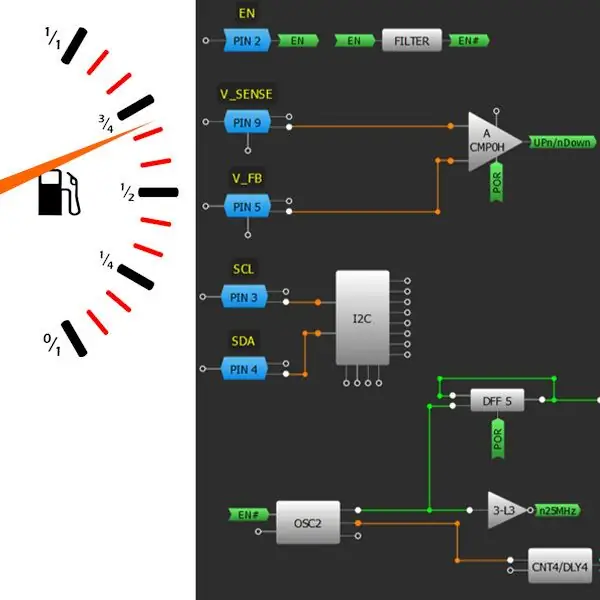

Krok 2: Vnútorný obvod

Flexibilný ADC je založený na dizajne uvedenom v Dialog Semiconductor AN-1177. Frekvencia hodín sa zvýši z 1 MHz na 12,5 MHz, aby sa mohol hodiny ADC počítať, pretože SLG46855 má k dispozícii hodiny 25 MHz. To umožňuje oveľa vyššiu rýchlosť aktualizácie pre jemnejšie rozlíšenie vzorky. LUT taktovanie dátových hodín ADC je zmenené, takže bude prechádzať signálom 12,5 MHz, keď je PWM DFF nízky.

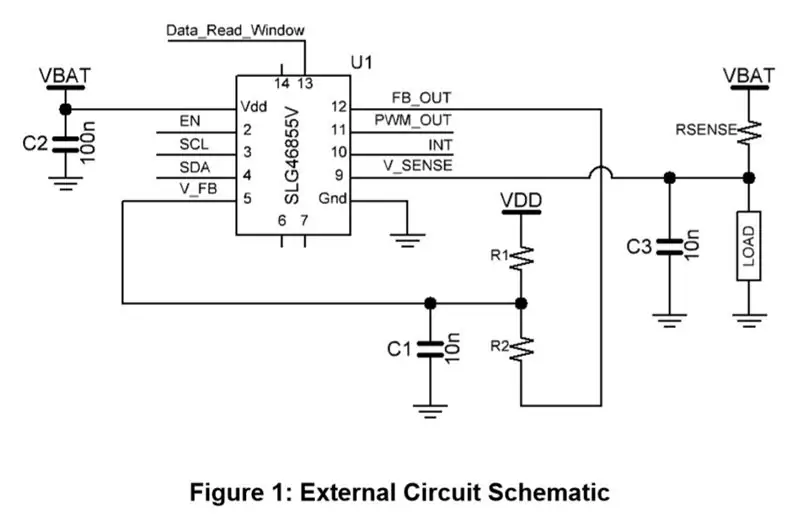

Krok 3: Externý obvod

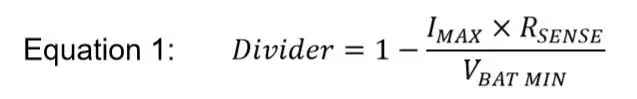

Sieť externých odporov a kondenzátorov sa používa na konverziu PWM na analógové napätie, ako je znázornené na schéme zapojenia na obrázku 1. Hodnoty sú vypočítané pre maximálne rozlíšenie pre maximálny prúd, ktorý zariadenie bude vnímať. Aby sme dosiahli túto flexibilitu, pridávame odpory R1 a R2 paralelne k VDD a uzemneniu. Odporový delič rozdeľuje VBAT na dolnú stranu rozsahu napätia. Pomer deliča pre očakávaný minimálny VBAT je možné vyriešiť pomocou rovnice 1.

Krok 4: I2C Prečítajte si pokyny

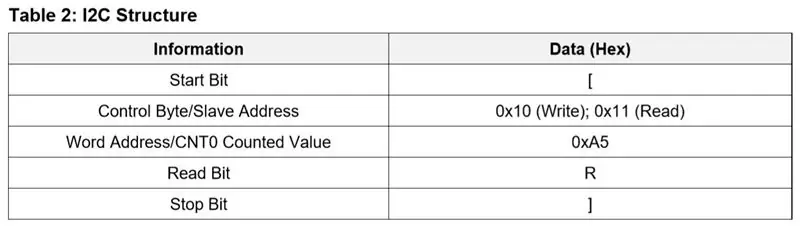

Tabuľka 1 popisuje štruktúru príkazov I2C na čítanie údajov uložených v CNT0. I2C príkazy vyžadujú štartovací bit, riadiaci bajt, adresu slova, bit na čítanie a stop bit.

Príklad príkazu I2C na čítanie hodnoty počítanej CNT0 je zapísaný nižšie:

[0x10 0xA5] [0x11 R]

Spočítaná hodnota, ktorá je prečítaná späť, bude hodnotou kódu ADC. Ako príklad je uvedený kód Arduino v súbore ZIP tejto poznámky k aplikácii na webovej stránke Dialogu.

Krok 5: Výsledky

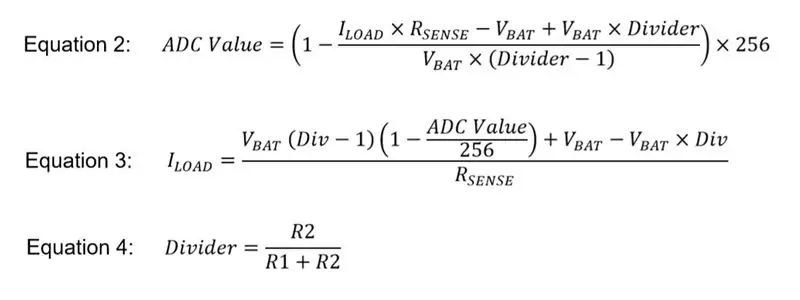

Na testovanie presnosti návrhu snímača prúdu ADC boli namerané hodnoty pri danom zaťažovacom prúde a úrovni VDD porovnané s teoretickou hodnotou. Teoretické hodnoty ADC boli vypočítané pomocou rovnice 2.

ILOAD, ktorý koreluje s hodnotou ADC, sa nachádza s rovnicou 3.

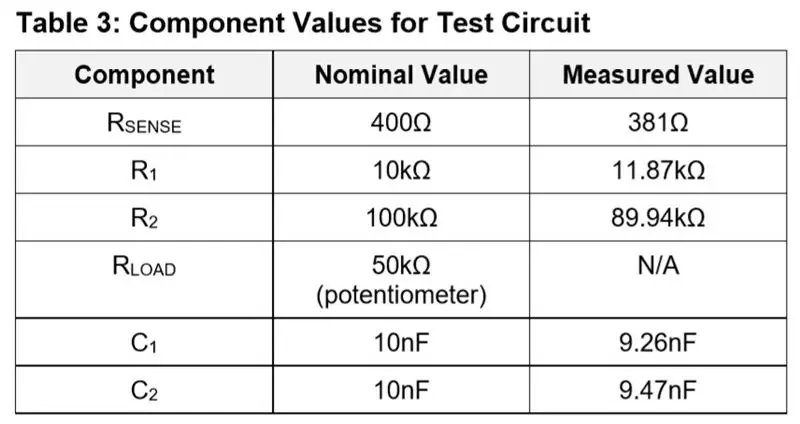

Na nasledujúce výsledky som použil tieto hodnoty zložiek uvedené v tabuľke 3.

Rozlíšenie prevodu hodnoty ADC na ILOAD je možné vypočítať pomocou rovnice 3 s nameranými hodnotami v tabuľke 2 a hodnotou ADC nastavenou na 1. Pri VBAT 3,9 V je rozlíšenie 4,96 µA/div.

Aby sa optimalizoval obvod snímania prúdu ADC na minimálnu úroveň VDD 3,6 V s maximálnym prúdom 1 100 µA a snímacím odporom 381 Ω, ideálny koeficient deliča by bol 0,884 na základe rovnice 1. S hodnotami uvedenými v tabuľke 2, skutočný delič má deliaci koeficient 0,876. Pretože je to o niečo menej, umožní to o niečo väčší rozsah zaťažovacieho prúdu, takže hodnoty ADC sú blízko celého rozsahu, ale nebudú pretekať. Skutočná hodnota deliča sa vypočíta podľa rovnice 4.

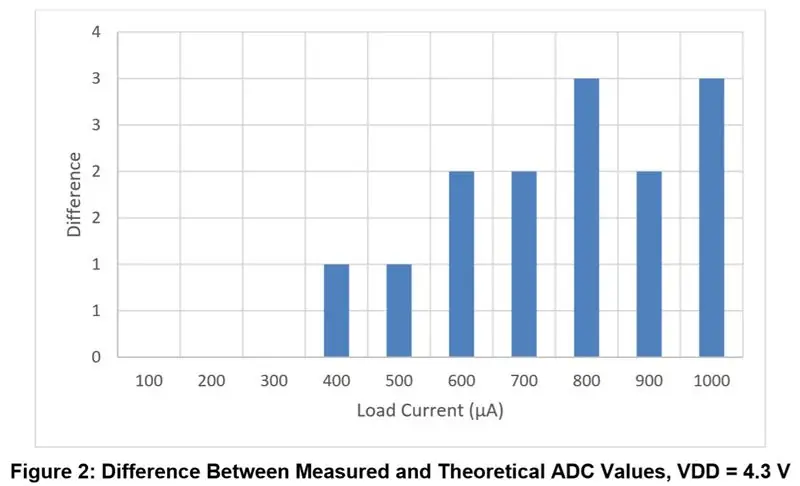

Vyššie (obrázky 2-6, tabuľky 4-6) sú uvedené merania obvodu pri troch úrovniach napätia: 4,3 V, 3,9 V a 3,6 V. Každá úroveň zobrazuje graf zobrazujúci rozdiel medzi nameranými a teoretickými hodnotami ADC. Teoretické hodnoty sa zaokrúhlia na najbližšie celé číslo. Existuje súhrnný graf na porovnanie rozdielov na troch úrovniach napätia. Potom je tu graf znázorňujúci koreláciu medzi teoretickými hodnotami ADC a prúdom záťaže na rôznych úrovniach napätia.

Záver

Zariadenie bolo testované na troch úrovniach napätia: 3,6 V, 3,9 V a 4,3 V. Rozsah týchto napätí modeluje plnú lítium -iónovú batériu, ktorá sa vybíja na nominálnu úroveň. Z troch úrovní napätia je zrejmé, že zariadenie bolo typicky presnejšie pri 3,9 V pre zvolený externý obvod. Rozdiel medzi nameranými a teoretickými hodnotami ADC bol iba 1 desatinná hodnota vypnutá pri záťažových prúdoch 700 - 1 000 µA. V danom rozsahu napätia boli namerané hodnoty ADC v najhoršom prípade o 3 desatinné miesta nad nominálnymi podmienkami. Na optimalizáciu rôznych úrovní napätia VDD je možné vykonať ďalšie úpravy odporového deliča.

Odporúča:

Ako nastaviť OSMC s Hyperion na Raspberry Pi s LED pásikom WS2812b: 8 krokov

Ako nastaviť OSMC s Hyperionom na Raspberry Pi s LED pásikom WS2812b: Niekedy viem veľmi dobre anglicky, niekedy nie … Ako prvé. Toto je môj prvý návod a angličtina nie je môj rodný jazyk, takže prosím, nebuďte na mňa príliš tvrdí. Toto nebude o tom, ako postaviť rám, to je jednoduché. Ide o inštaláciu

Ako nastaviť víno na Raspberry Pi: 8 krokov

Ako nastaviť víno na Raspberry Pi: Wine je úžasný nástroj, ktorý pomáha spúšťať aplikácie Windows v systémoch Linux, Ubuntu atď. Ak sa chcete dozvedieť všetky podrobnosti, navštívte stránku www.winehq.org (toto nie je pridružený odkaz) Ide o to, že všetky aplikácie pre Windows sú navrhnuté pre procesory s

Ako nastaviť Dotnet na Raspberry Pi: 5 krokov

Ako nastaviť Dotnet na Raspberry Pi: NET Framework na Raspberry Pi - čo to je a čo ešte PREČO? Spustenie Microsoft.NET Framework alebo tiež nazývaného iba Dotnet na Raspberry Pi znie na prvý pohľad trochu divne a zložito. Ale ukazuje sa to celkom múdre a rozumné v

Ako nastaviť frekvenciu procesora v systéme Windows 10: 5 krokov

Ako nastaviť frekvenciu procesora v systéme Windows 10: Toto ukazuje, ako nastaviť frekvenciu procesora, ako aj spomalenie/obmedzenie alebo odblokovanie plnej rýchlosti CPU na počítači so systémom Windows 10

Ako nastaviť Samsung Galaxy S7 v systéme Android 8.0 na zobrazenie iba obrazovky pre jednu aplikáciu !!: 5 krokov

Ako nastaviť Samsung Galaxy S7 s Androidom 8.0 tak, aby zobrazoval iba obrazovku pre jednu aplikáciu !!: Tento návod vám ukáže, ako nastaviť Samsung Galaxy S7 tak, aby zobrazoval obrazovku iba pre jednu aplikáciu. Je to skvelé, ak máte dieťa/dieťa kto sa rád hrá s vašim telefónom alebo sa chce uistiť, že váš telefón zostane v jednej aplikácii iba vtedy, keď je niekto iný