Obsah:

- Krok 1: Konfigurujte programovateľnú logiku Zynq pre vysielač

- Krok 2: Konfigurujte programovateľnú logiku Zynq pre prijímač

- Krok 3: Nastavte ovládač VDMA

- Krok 4: Nastavte sieť Nanorouter

- Krok 5: Nastavte systém spracovania Zynq na prenos údajov cez ethernet

- Krok 6: Nastavte systém spracovania Zynq na príjem dát cez ethernet

- Krok 7: Pripojte dosky Zybo k zdroju HDMI a umývadlu HDMI

- Krok 8: Alternatívne nápady na zlepšenie

- Krok 9: Prístupnosť

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 11:59.

- Naposledy zmenené 2025-01-23 15:06.

Túžili ste niekedy po tom, aby ste mohli televízor pripojiť k počítaču alebo prenosnému počítaču ako externý monitor, ale nechceli ste mať v ceste všetky tie otravné šnúry? Ak áno, tento návod je práve pre vás! Aj keď existuje niekoľko produktov, ktoré dosahujú tento cieľ, projekt pre domácich majstrov je oveľa uspokojivejší a potenciálne lacnejší.

Tento koncept sa líši od produktov, ako je chromecast, pretože má namiesto HDMI zariadenia namiesto streamovacieho zariadenia nahradiť kábel HDMI pripojený k monitoru.

Náš projekt bol vytvorený ako záverečný projekt pre kurz Operačné systémy v reálnom čase na Kalifornskej štátnej polytechnickej univerzite v San Luis Obispo.

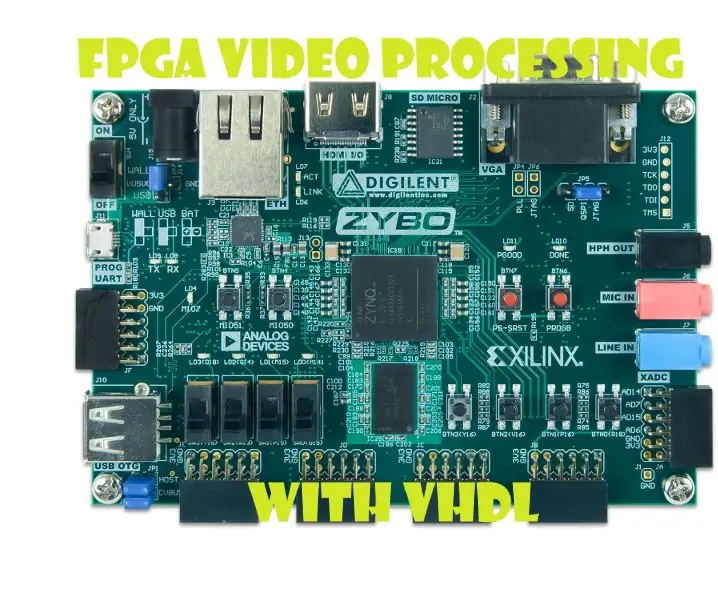

Cieľom projektu je využiť dve dosky Digilent Zybo, ktoré budú fungovať ako bezdrôtové komunikačné rozhranie medzi vysielacím zariadením HDMI (PC, blu-ray atď.) A prijímacím zariadením HDMI (stolný monitor, projektor, televízor atď.).

Jeden Digilent Zybo bude prepojený pomocou HDMI s vysielacím zariadením a druhý bude prepojený pomocou HDMI s prijímacím zariadením.

Bezdrôtová komunikácia bude prebiehať pomocou bezdrôtovej lokálnej siete vyhradenej pre vysielač a prijímač bez toho, aby bola smerovaná cez domáci router alebo iné podobné zariadenie. Bezdrôtový modul použitý na tento projekt je nanorutér tplink wr802n, z ktorých jeden funguje ako prístupový bod na vytvorenie siete a druhý slúži ako klient na pripojenie k sieti. Každý nanorouter bude pripojený pomocou ethernetového kábla k doske Zybo. Po pripojení k týmto smerovačom budú zariadenia komunikovať prostredníctvom protokolu TCP, ako keby boli pripojené jediným ethernetovým káblom (to znamená, že jedinou konfiguráciou potrebnou na vytvorenie pripojenia je adresa IP klienta).

Aj keď cieľom projektu bolo uľahčiť tok videa s rozlíšením 1080 x 720 pri 60 Hz, nebolo to možné dosiahnuť kvôli obmedzeniam šírky pásma v bezdrôtovej sieti a nedostatku kompresie videa v reálnom čase na zníženie údajov potrebných na odoslanie. Tento projekt namiesto toho slúži ako rámec pre budúci vývoj na dosiahnutie tohto cieľa, pretože má prísne obmedzené obmedzenia rýchlosti snímkovania na správne streamovanie údajov HDMI podľa plánu.

Požiadavky projektu:

2x vývojová doska Digilent Zybo (musí mať aspoň jeden port HDMI)

2x HDMI káble

2x mikrousb káble (na pripojenie Zybo k počítaču za účelom vývoja)

2x nanoradiče tplink wr802n (vrátane 2x napájacieho adaptéra pre microusb a nástennú zásuvku)

2x ethernetové káble

*** Poznámka: Tento tutoriál predpokladá znalosť sady návrhov Vivado a skúsenosti s vytváraním nového projektu a dizajnu bloku. ***

Krok 1: Konfigurujte programovateľnú logiku Zynq pre vysielač

Náš prístup k vývoju programovateľnej logiky vysielača bol vykonať prechod z počítača na monitor z počítača na monitor pomocou dvoch blokov VDMA (Video Direct Memory Access), jedného na zápis a druhého na čítanie.

Oba sú vybraté pre voľne spustený režim 3 rámcovej vyrovnávacej pamäte (0-1-2). Pretože je jadro videa optimalizované na 60 snímok za sekundu, znamená to, že VDMA bude zapisovať alebo čítať do nového rámca každých 16,67 ms v tomto poradí: 0, 1, 2, 0, 1, 2, 0, 1, 2. Umiestnenia pamäte DDR pre každý rámec sú pre tieto dva VDMA odlišné, pretože už nie sú navzájom synchronizované. Namiesto toho sa na synchronizáciu pohybu údajov medzi dvoma pamäťovými miestami používa hardvérový časovač (TTC1) nakonfigurovaný na 60 Hz.

Obrázok vyššie zobrazuje 3 snímky, ich rozmery a množstvo pamäte, ktoré každý vyžaduje (napravo od rámca). Ak priradíme zapisovaciu VDMA k týmto pamäťovým miestam, potom budeme môcť priradiť načítané pamäťové VDMA miesta nad rámec tejto sady, povedzme od 0x0B000000. Každý rámec má 1280*720 pixelov a každý pixel je tvorený 8 bitmi červenej, zelenej a modrej, čo je celkom 24 bitov. To znamená, že rámec pozostáva z 1 280*720*3 bajtov (2,76 MB).

Vnútri časovača IRQ, ktorý je popísaný v nastavení ovládača VDMA, bude pracovať s kopírovaním údajov medzi dvoma miestami pamäte VMDA. VDMA poskytuje ukazovateľ na aktuálny rámec, do ktorého sa zapisuje alebo z ktorého sa z neho číta. Rám je reprezentovaný konkrétnym šedým kódom, ktorý je skonvertovaný v softvéri. Definície sivého kódu pre konfiguráciu vyrovnávacej pamäte s 3 rámcami nájdete v produktovej príručke AXI VDMA v prílohe C.

To nám umožňuje skopírovať obsah zapísaný do pamäte bez čítania z rámca, do ktorého sa práve zapisuje.

*** Všimnite si toho, že načítaný VDMA sa nepoužíva pri odosielaní údajov prostredníctvom bezdrôtovej siete. Jeho jediným účelom je overiť správnu činnosť kopírovania pamäte zo zápisu VMDA. Čítaný VMDA by mal byť deaktivovaný. ***

Tu sú kroky k vytvoreniu bloku dizajnu vysielača:

- Pri vytváraní nového projektu je dobré k projektu priradiť čip alebo dosku. Tento odkaz popisuje, ako do adresára Vivado pridať nové súbory doštičiek a ako priradiť správnu dosku k vášmu projektu. Bude sa vám to hodiť pri pridávaní bloku Processing System a prechode z hardvéru na softvér (strana SDK).

-

Pridajte nasledujúce bloky:

- dvi2rgb

- Video v streame Axi4

- Ovládač časovania

- stream axi4, aby ste videli

- rgb2dvi

- AXI VDMA x2

- AXI GPIO x2

- Sprievodca hodinami

- Konštantný

- Systém spracovania Zynq

- Pri pridávaní systému spracovania kliknite na „Spustiť automatizáciu blokov“v hornom zelenom paneli a uistite sa, že je vybratá možnosť „Použiť predvoľbu dosky“. Nechajte všetko ostatné predvolené.

- Obrázky každého okna konfigurácie bloku nájdete na obrázkoch vyššie. Ak nevidíte obrázok pre konkrétne okno, nechajte ho ako predvolený.

-

Začnite s konfiguráciou systému Zynq Processing:

- V konfigurácii PS-PL AXI Non Secure Povoliť GP Master AXI, povoliť rozhranie M AXI GP0

- V konfigurácii PS-PL Rozhranie HP Slave AXI povoľte HP0 aj HP1

- V konfigurácii MIO Uistite sa, že je v časti I/O periférie povolená ENET0, potom jednotka aplikačného procesora, povoľte Timer0

- V konfigurácii hodín PL Fabric Clocks povoľte FCLK_CLK0 a nastavte na 100 MHz.

- Kliknite na Ok

- Pred kliknutím na položku „Spustiť automatizáciu pripojenia“pripojte videobloky tak, ako je to vidieť na obrázku dizajnu bloku TX vyššie. Budete chcieť premenovať konštantu na VDD a nastaviť hodnotu na 1. Pripojte zodpovedajúcim spôsobom video bloky.

- Vykonajte hodiny a dátové kolíky HDMI TMDS externé na blokoch rgb2dvi a dvi2rgb

- Vytvorte vstupný a výstupný port pre signál detekcie horúcej zástrčky (HPD) a spojte ich dohromady, tieto sú definované v súbore obmedzení

-

Hodiny pixelov sa obnovia z TMDS_Clk_p, ktorý je vytvorený v súbore obmedzení. To bude 74,25 MHz v súlade s rozlíšením 720p. Je dôležité pripojiť hodiny pixelov (z bloku dvi2rgb) k nasledujúcim pinom:

- vid_io_in_clk (blokovanie streamu vid in to axi)

- vid_io_out_clk (stream axi do bloku vid out)

- clk (ovládač časovania)

- PixelClk (rgb2dvi)

- *** Poznámka: Aby bolo možné aktivovať obnovu pixelových hodín, v súčasnej dobe musia byť konektory HDMI rx a tx zapojené do aktívneho zdroja/drezu. Jedným zo spôsobov, ako to obísť, je oddeliť bloky video rx a tx do rôznych hodinových domén (inými slovami, vygenerujte nové hodiny 74,25 MHz, ktoré sa budú napájať do bloku tx). ***

- Potom nastavte sprievodcu hodinami tak, aby ste mali vstup 100 MHz (globálny zdroj vyrovnávacej pamäte) a 3 výstupné takty @ 50 MHz (hodiny AXI-Lite), 150 MHz (hodiny AXI4-Stream), 200 MHz (pin dvi2rgb RefClk).

- Pripojte pin systému spracovania FCLK_CLK0 k vstupu sprievodcu hodinami

- V tomto okamihu kliknite na „Spustiť automatizáciu pripojenia“na zelenom paneli v hornej časti okna návrhu. Je dobré to urobiť po jednom bloku a postupovať podľa obrázka návrhu bloku TX vyššie.

- Nástroj sa pokúsi pridať prepojenie AXI, ktoré funguje ako prepojenie master/slave pre bloky, ktoré používajú zbernicu AXI-Lite (VDMA a GPIO).

- Pridá tiež AXI SmartConnect, ktorý funguje ako prepojenie master/slave pre rozhrania AXI4-Stream a High Performance procesor používané VDMA (Stream to Memory Map a naopak).

- Nástroj tiež pridá Obnovenie systému procesora. Uistite sa, že je pripojený iba k blokom VDMA, GPIO a procesorom. Nepripájajte ho k žiadnym video blokom (t. J. Dvi2rgb, časovač, videostream atď.)

- Po dokončení automatizácie pripojenia overte, či sa pripojenia zhodujú s obrázkom návrhu bloku TX. Všimnete si ďalší blok System ILA, ktorý nebol spomenutý. Toto je len na ladenie a zatiaľ to nie je potrebné. Používa 150M reset procesora, takže to nie je ani potrebné. Kdekoľvek vidíte malé zelené „chyby“na autobusoch, je to kvôli ILA a môžu byť ignorované.

- Posledným krokom je kliknutie pravým tlačidlom na návrh bloku v strome zdrojov projektu a zvoľte „Vytvoriť HDL Wrapper“. Ak plánujete do obálky pridať logiku, bude prepísaná vždy, keď je vybratá.

- Bližšie informácie o strane SDK nájdete v časti Nastavenie ovládača VDMA.

Hodiny a reset

Zistil som, že najdôležitejším aspektom akéhokoľvek projektu programovateľnej logiky je starostlivé zváženie domén hodín a resetovacích signálov. Ak sú správne nakonfigurované, máte dobrý predpoklad na to, aby váš návrh fungoval.

Pixel hodiny a časovanie sú zablokované

Aby sa overilo, že určité signály sú aktívne, je vhodné prepojiť tieto signály s diódami LED (hodiny, resety, zámky atď.). Dva signály, ktoré som považoval za užitočné sledovať na doske vysielača, boli pixelové hodiny a „uzamknutý“signál v bloku výstupu signálu AXI4-Stream do videa, ktorý vám hovorí, že načasovanie videa bolo synchronizované s ovládačom časovania a zdrojom videa. údaje. Pridal som nejakú logiku do obalového bloku dizajnu, ktorý sleduje hodiny pixelov pomocou signálu PixelClkLocked na bloku dvi2rgb ako reset. Tu som priložil súbor ako hdmi_wrapper.v. Tu je priložený aj súbor obmedzení.

Krok 2: Konfigurujte programovateľnú logiku Zynq pre prijímač

Programovateľný logický blok pre prijímač je jednoduchší. Kľúčovým rozdielom okrem chýbajúcich vstupných blokov hdmi je absencia obnovených hodín pixelov. Z tohto dôvodu musíme vygenerovať vlastné z hodinového sprievodcu. Tento návrh by sa mal vykonať v samostatnom projekte od vysielača. Na naše účely projekt prijímača sledoval dosku Zybo 7Z-20, zatiaľ čo vysielač nasledoval dosku Z7-10. FPGA na doskách sú rôzne, takže … buďte opatrní.

Tu sú kroky k vytvoreniu bloku návrhu prijímača:

-

Pridajte do svojho návrhu nasledujúce bloky ip:

- Ovládač časovania

- Výstup AXI4-stream na video

- RGB na DVI

- AXI VDMA

- AXI GPIO

- Systém spracovania

- Sprievodca hodinami

- Konštantná (VDD nastavená na 1)

- Pri konfigurácii týchto blokov postupujte rovnako ako pri vysielači. Tu sú zahrnuté obrázky s výraznými rozdielmi v konfigurácii. Ostatné zostávajú rovnaké ako vysielač.

- Nakonfigurujte VDMA pre tento dizajn iba ako kanál na čítanie. Vypnite zapisovací kanál.

-

Sprievodca hodinami by mal byť nakonfigurovaný pre nasledujúce výstupy:

- clk_out1: 75 MHz (takt pixelov)

- clk_out2: 150 MHz (taktovací tok)

- clk_out3: 50 MHz (hodiny axi-lite)

- Pripojte videobloky podľa obrázku na obrázku bloku RX.

- Potom spustite automatizáciu pripojenia, ktorá pridá bloky AXI Interconnect, AXI SmartConnect a System Reset a pokúsi sa vytvoriť vhodné pripojenia. Choďte sem pomaly, aby ste sa presvedčili, že nevykonáva nechcené pripojenia.

- V bloku rgb2dvi urobte hodiny a dátové piny HDMI TMDS externé

- V tomto prevedení nie je potrebný signál za behu.

Krok 3: Nastavte ovládač VDMA

Nastavenie pre rôzne bloky, ktoré sú konfigurované prostredníctvom rozhrania AXI-Lite, sa najlepšie vykoná pomocou referenčných projektov zahrnutých v BSP. Po exporte návrhového hardvéru a spustení súpravy SDK z Vivado budete chcieť pridať nový balík podpory dosky a zahrnúť knižnicu lwip202 do okna nastavení BSP. Otvorte súbor systému.mss z BSP a uvidíte prítomné periférne ovládače z vášho návrhu bloku. Voľba „Príklady importu“vám umožňuje importovať demo projekty, ktoré využívajú tieto periférie, a tak vám ukáže, ako ich konfigurovať v softvéri pomocou dostupných ovládačov Xilinx (pozri priložený obrázok).

Toto bola metóda používaná na konfiguráciu VDMA, časovača a prerušenia a GPIO. Tu bol zahrnutý zdrojový kód prenosu aj príjmu. Rozdiely sú takmer výlučne v main.c.

*** POZNÁMKA: Keďže v čase písania tohto tutoriálu systém nie je úplne funkčný, zdrojový kód v tejto časti neobsahuje kód bezdrôtovej siete. V dôsledku kombinácie projektov jadra prenosu/príjmu video jadra s projektmi prenosu/príjmu siete je potrebné vyriešiť niekoľko chýb. Tento tutoriál s nimi preto zatiaľ zaobchádza oddelene. ***

Funkcia obsluhy prerušenia TX (IRQHandler)

Táto funkcia číta sivé kódy poskytované VDMA na čítanie aj zápis prostredníctvom blokov GPIO. Šedé kódy sa prevedú na desatinné miesta a použijú sa na výber umiestnenia základnej pamäte rámca aktuálneho rámca. Skopírovaný rámec je predchádzajúcim rámcom do rámca, do ktorého zapisuje VDMA (napr. Ak VDMA zapisuje do rámca 2, skopírujeme rámček 1; ak zapisujete do rámca 0, zabalíme a čítame z rámca 2).

Táto funkcia zachytáva iba každý 6. snímok, aby sa znížila snímková frekvencia na 10 Hz namiesto 60 Hz. Horná hranica siete je 300 Mbps. Pri rýchlosti 10 snímok za sekundu je potrebná šírka pásma 221,2 Mb / s.

Komentovanie/zrušenie komentovania dvoch riadkov v tejto funkcii umožní užívateľovi prejsť do režimu HDMI passthru na účely ladenia/testu (kód je označený, aby označil príslušné riadky). Aktuálne skopíruje rámec do pamäte, ktorú používa ethernetový kód.

Funkcia obsluhy prerušenia RX (IRQHandler)

Táto funkcia je veľmi podobná funkcii TX, ale kopíruje z 2 vyrovnávacej pamäte FIFO, ktorú ethernet používa na zápis prichádzajúcich údajov. Ethernetový kód označuje, do ktorého rámca sa zapisuje do FIFO, dáta sa kopírujú z opačného rámca. Údaje sa skopírujú do rámca priamo za rámec, ktorý číta VDMA, aby sa zabránilo roztrhnutiu.

Krok 4: Nastavte sieť Nanorouter

Ak chcete vytvoriť sieť pomocou nanorouterov TPlink, zapnite ich jednotlivo a pripojte sa k predvolenému wifi SSID pre zariadenia. Viac informácií o konfiguračných nastaveniach tohto konkrétneho zariadenia nájdete v používateľskej príručke zariadenia.

Nastavte jedno zo zariadení ako prístupový bod, ktorý bude fungovať ako primárne pripojenie k sieti. Nezabudnite pomenovať sieť a zaznamenať jej názov a vypnúť DHCP (nechceme, aby smerovač dynamicky konfiguroval adresy IP, chceme, aby dosky Zybo vysielača a prijímača nastavovali svoje adresy IP sami, aby boli konzistentné). Po konfigurácii sa uistite, že sa zariadenie reštartuje a vytvorí túto sieť.

Nastavte druhé zariadenie ako klienta a uistite sa, že sa pripája k sieťovému SSID, ktorý ste nastavili pomocou prvého nanoroutera. Ešte raz sa uistite, že je klient DHCP zakázaný.

Akonáhle klient skončí a reštartuje sa, mal by sa pripojiť k nanorutoru prístupového bodu (ak nie, pravdepodobne je problém vo vašej konfigurácii jedného zo zariadení). Po pripojení k prístupovému bodu si všimnete, že LED dióda na klientovi bude neprerušovane svietiť.

V tomto mieste bude nanorouter LED diódy prístupového bodu pravdepodobne naďalej blikať, to je v poriadku! Blikajúca kontrolka znamená, že nie je pripojený k inému zariadeniu z ethernetového portu, a akonáhle je pripojený k nakonfigurovanému Zybo, LED dióda zostane svietiť, čo znamená úspešné pripojenie k sieti.

Teraz, keď máme nastavené naše nanoroutery, máme bezdrôtovú sieť, ktorá nám umožní komunikovať prostredníctvom. Dôležitou poznámkou je, že naša metóda konfigurácie pre nanorutery (ako prístupový bod a klient) nám umožňuje komunikovať z vysielacej dosky Zybo na prijímaciu dosku Zybo, ako keby boli tieto dva prepojené jediným ethernetovým vodičom. To robí naše nastavenie siete menej náročným, pretože alternatíva by pravdepodobne zahŕňala konfiguráciu dosiek Zybo na explicitné pripojenie k serveru spolu s predpokladaným pripojením.

Akonáhle sú obe zariadenia nastavené, nanorutery sú nakonfigurované a pripravené na implementáciu do vašej siete WIDI. Neexistuje žiadne špecifické párovanie medzi nanoroutermi a doskami Zybo, pretože prístupový bod alebo klient bude fungovať buď pre vysielacie alebo prijímacie zariadenie.

Krok 5: Nastavte systém spracovania Zynq na prenos údajov cez ethernet

Aby sme mohli prenášať údaje HDMI z jednej dosky Zybo na druhú, musíme do nášho ovládača VDMA začleniť protokol Ethernet. Našim cieľom je streamovať jednotlivé video snímky cez periférne zariadenie Ethernet v systéme spracovania nastavenou rýchlosťou, ktorá je v súlade s našou šírkou pásma siete. Pre náš projekt sme použili TCP poskytovaný holým kovom LwIP API. Pretože obaja členovia projektu majú relatívne málo skúseností so sieťovými nástrojmi, táto voľba bola vykonaná bez úplného uznania dôsledkov a obmedzení spojených s TCP. Hlavným problémom tejto implementácie bola obmedzená šírka pásma a skutočnosť, že skutočne nie je navrhnutá na naparovanie veľkého objemu dát. Alternatívne riešenia na nahradenie TCP a zlepšenie tbe v tomto projekte budú prediskutované neskôr.

Stručný popis TCP s LwIP: Dáta sú odosielané po sieti v paketoch veľkosti tcp_mss (maximálna veľkosť segmentu TCP), ktorá je spravidla 1460 bajtov. Volanie tcp_write bude vyžadovať určité údaje, na ktoré odkazuje ukazovateľ, a nakonfigurovať pbufs (vyrovnávacie pamäte paketov) tak, aby uchovávali údaje a poskytovali štruktúru operácií TCP. Maximálne množstvo údajov, ktoré je možné zaradiť do frontu naraz, je nastavené ako tcp_snd_buf (priestor vyrovnávacej pamäte odosielateľa TCP). Pretože tento parameter je 16 bitové číslo, obmedzujeme sa na veľkosť vyrovnávacej pamäte odosielania 59695 bajtov (vo vyrovnávacej pamäti odosielania je určité požadované vypchávky). Hneď ako sú dáta zaradené do frontu, zavolá sa tcp_output, aby sa dáta začali prenášať. Pred odoslaním ďalšieho segmentu údajov je nevyhnutné, aby boli všetky predchádzajúce pakety úspešne odoslané. Tento proces sa vykonáva pomocou funkcie recv_callback, pretože je to funkcia, ktorá sa volá, keď je z prijímača vidieť potvrdenie.

Použitie príkladov projektov v súprave Vivado SDK je veľmi nápomocné pri učení sa operácie LwIP TCP a je dobrým východiskovým bodom pre začiatok nového projektu.

Postup pre prenosové zariadenie WiDi je nasledujúci:

- Inicializujte sieť TCP pomocou volania funkcie holého kovu ovládača LWIP.

- Zadajte všetky funkcie spätného volania potrebné pre sieťové operácie.

- Pripojte sa k prijímaču WiDi pripojením k jeho IP adrese a portu (naša konfigurácia: IP prijímača je 192.168.0.9, pripojte sa k portu 7).

- Po vypršaní časovača ovládača VDMA zadajte TX ISR.

- Na základe sivého kódu VDMA určte aktuálny rámec vyrovnávacej pamäte pre prístup

- Zaraďte do poradia prvý segment údajov vo vyrovnávacej pamäti odosielania TCP

- Vytvorte výstup údajov a aktualizujte miestne premenné, aby ste mali prehľad o tom, koľko údajov bolo odoslaných z aktuálneho rámca.

- Po dosiahnutí prijatého spätného volania (volanie funkcie uskutočnené potom, čo vysielač dostane potvrdenie o načítaní údajov), zaraďte do radu ďalší segment údajov.

- Kroky 7 a 8 opakujte, kým nebude odoslaný celý rámec.

- Vráťte sa do pokojového stavu, aby ste počkali na ďalšie prerušenie časovača, čím indikujete, že je nový rámec pripravený (Späť na krok 4).

Nezabudnite nastaviť nastavenia LwIP balíka podpory dosky, ako je znázornené na obrázku vyššie. Všetky hodnoty sú predvolené okrem tcp_snd_buf, tcp_pueue_ooseq, mem_size, memp_n_tcp_seg. Všimnite si tiež, že podrobné ladenie je možné dosiahnuť zmenou parametrov BSP pre skupinu debug_options.

Krok 6: Nastavte systém spracovania Zynq na príjem dát cez ethernet

Vývojová doska Zybo, ktorá bude fungovať ako bezdrôtový prijímač, bude fungovať podobne ako vysielacie zariadenie. Nastavenia balíka podpory dosky pre LwIP budú rovnaké ako v predchádzajúcom kroku.

Zariadenie zachytí pakety obsahujúce segmenty video rámca z nanorutera a skopíruje údaje rámca videa do medzipamäte trojitého rámca pre prijímajúci VDMA. Aby sa predišlo prepisovaniu akýchkoľvek údajov, používa sa pri zbere dát z nanorouteru dvojitá dátová vyrovnávacia pamäť (budeme ju označovať ako sieťová vyrovnávacia pamäť), takže sieťová prevádzka môže pokračovať v streamovaní, zatiaľ čo predchádzajúci celý rámec videa sa kopíruje do Vyrovnávacia pamäť VDMA.

Procedúra pre prijímacie zariadenie WiDi vyžaduje dve úlohy, z ktorých jedna prijíma ethernetové údaje a druhá kopíruje video snímky zo sieťovej vyrovnávacej pamäte do vyrovnávacej pamäte s trojitým rámcom VDMA.

Úloha príjmu ethernetu:

- Inicializujte sieť TCP pomocou holých kovových volaní funkcií ovládača LWIP (nastavenie pomocou adresy IP, ku ktorej sa bude vysielač pripájať, 192.168.0.9 v našej)

- Zadajte všetky funkcie spätného volania potrebné pre sieťové operácie.

- Po prijatí ethernetového paketu skopírujte údaje paketu do aktuálnej sieťovej vyrovnávacej pamäte a zvýšte aktuálne nahromadené údaje.

- Ak paket vypĺňa vyrovnávaciu pamäť rámca siete, pokračujte krokmi 5 a 6. V opačnom prípade sa vráťte k kroku 3 od tejto úlohy.

- signál, že úloha vyrovnávacej pamäte s trojitým rámcom VDMA by sa mala skopírovať z novo dokončenej sieťovej vyrovnávacej pamäte.

- Prepnite na inú sieťovú vyrovnávaciu pamäť a pokračujte v zhromažďovaní údajov prostredníctvom ethernetu.

- Nečinnosť, kým sa neprijme nový ethernetový paket (krok 3).

Skopírujte sieťovú vyrovnávaciu pamäť do trojitej vyrovnávacej pamäte VDMA:

- Po vypršaní časovača ovládača VDMA zadajte RX ISR.

- Na základe sivého kódu VDMA určte prístup k aktuálnej vyrovnávacej pamäti rámcov.

- Zistite, ktorá sieťová vyrovnávacia pamäť sa skopíruje do vyrovnávacej pamäte VDMA, a skopírujte tieto údaje

Krok 7: Pripojte dosky Zybo k zdroju HDMI a umývadlu HDMI

Teraz pripojte káble hdmi k prijímaču a vysielaču, naprogramujte FPGA a spustite systém spracovania. Snímková frekvencia bude pravdepodobne veľmi pomalá kvôli obrovskej réžii v prevádzke LwIP a obmedzenej šírke pásma. Ak existujú nejaké problémy, pripojte sa cez UART a pokúste sa identifikovať všetky varovania alebo chyby.

Krok 8: Alternatívne nápady na zlepšenie

Veľkým problémom tohto projektu bolo množstvo údajov potrebných na odoslanie cez wifi. Očakávalo sa to, ale podcenili sme vplyv, ktorý to bude mať, a vyústilo to skôr do série obrazov na obrazovke, ako do kanála videa. Existuje niekoľko spôsobov, ako zlepšiť tento projekt:

- Kompresia videa v reálnom čase. Kompresia prichádzajúceho kanála videa po snímke by výrazne znížila množstvo údajov, ktoré je potrebné odoslať cez sieť. V ideálnom prípade by sa to malo vykonať v hardvéri (čo nie je ľahká úloha) alebo by to bolo možné vykonať v softvéri pomocou iného jadra ARM na spustenie kompresných algoritmov (to by vyžadovalo ďalšiu analýzu, aby sa zabezpečilo, že načasovanie vyjde). Na webe sme našli niekoľko komponentov na kompresiu videa v reálnom čase s otvoreným zdrojovým kódom, ale väčšina z nich je IP.

- Implementácia ethernetového toku v hardvéri, nie v softvéri. Tam bolo veľa réžie kvôli nedostatku miesta, ktoré je k dispozícii na zaradenie odchádzajúcich údajov do vysielača, kvôli obmedzeniu veľkosti segmentu. Oveľa efektívnejším procesom je použiť AXI Ethernet IP na prenos údajov do vyrovnávacej pamäte FIFO alebo DMA. Tým by sa znížila dodatočná batožina z LwIP TCP a umožnil by sa väčší tok údajov.

Krok 9: Prístupnosť

Výsledným produktom tohto projektu WiDi by mala byť plne integrovaná, kompaktná dvojica zariadení, ktoré by používateľ mohol pripojiť k akémukoľvek zdroju HDMI a potom bezdrôtovo previesť video na displej s možnosťou HDMI. Zariadenie bude obsahovať SoC Zynq-7000, ktorý sa nachádza na referenčnej doske Zybo, a bude obsahovať sieťový hardvér, ktorý sa nachádza v nanoradičoch TP-Link. V ideálnom prípade by užívateľ bol schopný ovládať vysielací modul z diskrétneho miesta v cieľovom operačnom systéme s malou potrebou významných technických schopností.

Zabezpečenie a konektivita

Zariadenia by mali tiež obsahovať zabezpečenie TLS (Transport Layer Security) a mali by mať obmedzené možnosti automatického pripojenia, a to z dôvodu ochrany osobných údajov. Zámerom dizajnérov je, aby spojenie s displejom cez bezdrôtové rozhranie bolo zámerným krokom v mene používateľa, aby sa zabránilo omylu v vysielaní citlivého materiálu.

Súčasný stav

Do tohto bodu je stav projektu stále veľmi nedokončený. Aby mohol terajší užívateľ koncového bodu ťažiť z tohto tutoriálu, musí dobre ovládať technické znalosti návrhu vstavaného systému a musí mať určitú znalosť spolupráce programovateľného hardvéru a vstavaného softvéru.

Dáta odosielané cez sieť v tomto mieste nie sú šifrované a predpokladá sa, že ide o čistý prenos paketov TCP/IP.

Projekt jadra videa bol úspešne testovaný na prenos aj príjem. Na druhej strane bolo vytvorené bezdrôtové spojenie medzi dvoma doskami zybo a údaje testovacieho rámca boli úspešne odoslané. Stále je však potrebné skombinovať sieťový kód s každým jadrovým projektom videa a otestovať prenos skutočných video rámcov.

Odporúča:

DIY ESP32 Development Board - ESPer: 5 krokov (s obrázkami)

DIY ESP32 Development Board - ESPer: Nedávno som teda čítal o veľa IoT (Internet of Things) a verte mi, jednoducho som sa nevedel dočkať, kedy otestujem jedno z týchto nádherných zariadení s možnosťou pripojenia na internet, seba a dostávam ruky do práce. Našťastie príležitosť

Prepínanie svetiel ovládané pomocou žmurkania pomocou okuliarov na ochranu hlavy Shota Aizawa (My Hero Academia): 8 krokov (s obrázkami)

Prepínanie svetiel ovládané pomocou žmurkania pomocou okuliarov Shota Aizawa s gumovými hlavami (My Hero Academia): Ak čítate mangu mojej hrdinskej akademickej obce alebo sledujete anime z mojej hrdinskej akademickej obce, musíte poznať znak s názvom shota aizawa. Shota Aizawa, tiež známa ako gumová hlava, je profesionálnym hrdinom a učiteľom v homeroom triedy U-Class 1-A. Shota's Quirk mu dáva Ab

JALPIC One Development Board: 5 krokov (s obrázkami)

Vývojová rada JALPIC One: Ak sledujete moje projekty Instructables, viete, že som veľkým fanúšikom programovacieho jazyka JAL v kombinácii s mikrokontrolérom PIC. JAL je programovací jazyk podobný jazyku Pascal vyvinutý pre 8-bitové mikrokontroléry PIC spoločnosti Microchip. Mo

Spracovanie videa pomocou VHDL a Zybo: 10 krokov

Spracovanie videa pomocou VHDL a Zybo: FPGA sú na spracovanie rýchlejšie ako CPU, pretože môžu vykonávať mnoho paralelných výpočtov Poznámka: Tento projekt je stále vo výstavbe a bude sa zlepšovať (hneď ako budem mať čas). Medzitým cestujem po svete

Kvadrokoptéra využívajúca dosku Zybo Zynq-7000: 5 krokov

Quadcopter používajúci dosku Zybo Zynq-7000: Než začneme, tu sú niektoré veci, ktoré by ste chceli k projektu: Zoznam dielov 1 x doska Digilent Zybo Zynq-7000 1x rám kvadrokoptéry schopný pripojiť Zybo (pripojený súbor Adobe Illustrator pre laserové rezanie) 4x Turnigy D3530/ 14 Bezkartáčových motorov 1100KV 4x