Obsah:

- Krok 1: Vytvorenie zdrojového súboru modulu PWM

- Krok 2: Zostavenie modulu PWM- nastavenie Vivado

- Krok 3: Zostavenie modulu PWM- vytvorte súbor projektu

- Krok 4: Budovanie modulu PWM- návrh bloku bloku a nastavenie súboru obmedzenia (I)

- Krok 5: Budovanie modulu PWM- návrh bloku bloku a nastavenie súboru obmedzenia (II)

- Krok 6: Budovanie modulu PWM- návrh bloku bloku a nastavenie súboru obmedzenia (III)

- Krok 7: Budovanie modulu PWM- návrh bloku bloku a nastavenie súboru obmedzenia (IV)

- Krok 8: Budovanie modulu PWM- návrh bloku bloku a nastavenie súboru obmedzenia (V)

- Krok 9: Zostavenie modulu PWM- inštalácia hardvéru

- Krok 10: Zostavenie modulu PWM- generujte bitstream a spustite SDK

- Krok 11: Zostavenie modulu PWM- vytvorte novú aplikáciu v súprave Xilinx SDK

- Krok 12: Zostavenie modulu PWM- prehľad programu Explorer (I)

- Krok 13: Zostavenie modulu PWM- prehľad programu Explorer (II)

- Krok 14: Zostavenie modulu PWM- prehľad programu Explorer (III)

- Krok 15: Zostavenie modulu PWM- Zbaľte funkciu PWM (I)

- Krok 16: Zostavenie modulu PWM- Zbaľte funkciu PWM (II)

- Krok 17: Zostavenie modulu PWM- Zbaľte funkciu PWM (III)

- Krok 18: Zostavenie modulu PWM- spustite ho

- Krok 19: Spracovanie streamovaného videa na zariadení Digilent ZYBO s OV7670

- Krok 20: Kompletný blokový diagram

- Krok 21: Pripojte OV7670 k ZYBO

- Krok 22: Vytvorte návrh bloku

- Krok 23: Pridajte súbory VHDL pre ovládanie a snímanie kamery OV7670

- Krok 24: Pridajte súbor obmedzení

- Krok 25: Pridajte IP Repo pre HLS IP

- Krok 26: Pridajte moduly a IP

- Krok 27: Nastavenia konfigurácie IP

- Krok 28: Pridajte a nakonfigurujte blok IP IP

- Krok 29: Časť 1. Zostavenie modulu PWM pre servomotory

- Krok 30: Pripojenia bočného vstupu videa (zvýraznené)

- Krok 31: Pripojenia k OV7670

- Krok 32: Pripojenia na strane výstupu videa

- Krok 33: Spustite automatizáciu blokov a pripojení

- Krok 34: Vytvorte obalový program HDL

- Krok 35: Generujte bitstream, exportujte hardvér do SDK, spustite SDK z Vivado

- Krok 36: SDK (žiadne FreeRTOS)

- Krok 37: Implementácia FreeRTOS

- Krok 38: Pokyny na použitie

- Krok 39: Referencie a odkazy

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 12:01.

- Naposledy zmenené 2025-01-23 15:06.

Začnite od prvého kroku, kde nájdete podrobnosti o vytváraní 2-osového servopohonu PWM.

Začnite s rozsiahlym blokovým diagramom (krok 19), kde nájdete celý projekt.

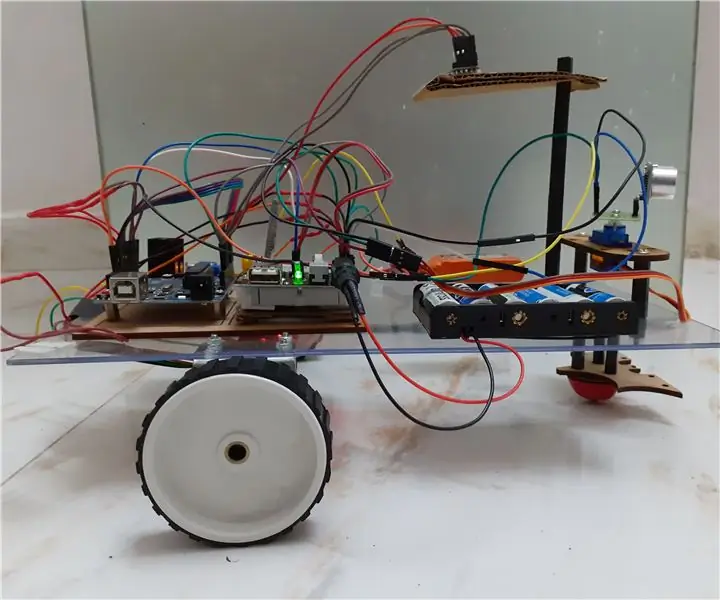

Použili sme nastavenie kamery + posunu/naklonenia:

Na pripojenie serva bol použitý modul PmodCON3 od spoločnosti Digilent.

Krok 1: Vytvorenie zdrojového súboru modulu PWM

Krok 2: Zostavenie modulu PWM- nastavenie Vivado

Najprv si stiahnite Vivado Design Suite z webu Xilinx. Nainštalujte si celú sadu návrhov vrátane súpravy Vivado Software Development Kit (SDK). Tento projekt používa verziu 2017.2.

Medzitým by mal byť nainštalovaný aj Digilent Adept 2 ako ovládač dosky Zybo.

Krok 3: Zostavenie modulu PWM- vytvorte súbor projektu

Pred vytvorením súboru projektu by ste sa mali uistiť, že ste už správne nainštalovali súbor Zybo ako návod tu:

Inštalácia súboru tabule Vivado verzie 2015.1 a novšej

Otvorené Vivado 2017.2. Na Rýchlom štarte kliknite na Vytvoriť projekt -> Ďalej -> Názov projektu (tu zadajte názov projektu) -> Typ projektu. Na Typ projektu zvoľte Projekt RTL a označte „Nešpecifikujte teraz zdroje“. Ďalej v predvolenej časti vyberte ako zobrazované meno „Dosky“a „Zybo“. Ďalej kliknutím na tlačidlo Dokončiť spustíte projekt.

Krok 4: Budovanie modulu PWM- návrh bloku bloku a nastavenie súboru obmedzenia (I)

V aplikácii Flow Navigator kliknite na položku „Vytvoriť návrh bloku“a potom kliknite na tlačidlo OK. kliknutím na znamienko „+“pridajte potrebné adresy IP. Pridať:

- Jeden systém spracovania ZYNQ7 Dva časovače AXI

- Dva časovače AXI

Krok 5: Budovanie modulu PWM- návrh bloku bloku a nastavenie súboru obmedzenia (II)

Po pridaní adries IP spustite automatizáciu blokov a automatizáciu pripojenia. Akonáhle je automatizácia dokončená, v bloku „axi_timer_0“kliknite pravým tlačidlom na pwm0 -> Vytvoriť externý. Externý pin pwm0 pomenujte ako pwm_Xaxis. Vyššie uvedený postup zopakujte aj v bloku „axi_timer_1“a externý kolík pwm0 pomenujte ako pwm_Zaxis.

Krok 6: Budovanie modulu PWM- návrh bloku bloku a nastavenie súboru obmedzenia (III)

Všimnite si toho, že zakaždým, keď dokončíme Block Design vo Vivado, musíme vytvoriť HDL Wrapper. Pretože to bude modul najvyššej úrovne pre každý projekt.

Krok 7: Budovanie modulu PWM- návrh bloku bloku a nastavenie súboru obmedzenia (IV)

Teraz musíme nastaviť náš súbor obmedzení na priradenie pinov pripojených k nášmu blokovému diagramu. Zatvorte okno Návrh bloku, na karte Zdroje „Pridať zdroje“-> Pridať alebo vytvoriť obmedzenia-> pridať súbor Zybo-Master.xdc ako naše súbory s obmedzeniami.

Krok 8: Budovanie modulu PWM- návrh bloku bloku a nastavenie súboru obmedzenia (V)

Otvorte obmedzujúci súbor Zybo-Master.xdc v priečinku Constraints, odkomentujte porty, ktoré chceme špecifikovať ako výstupné signály, a premenujte „get_ports {XXXX}“, ktorý XXXX označuje externý pin pomenovaný v blokovom diagrame. Nastavenie súboru obmedzení je znázornené na obrázku.

Krok 9: Zostavenie modulu PWM- inštalácia hardvéru

Pripojte servomotory k Pmod CON3. TowerPro SG90 je model servomotora, ktorý sme použili v tomto projekte. Oranžový vodič pre vodiče servomotora predstavuje signál PWM, pripojený na pin SIG v Pmod CON3. Červený vodič Vcc je napájací vodič pripojený k kolíku VS v Pmod CON3. Nakoniec je hnedý vodič Gnd uzemňovací vodič pripojený k kolíku GND. Potom vložte Pmod CON3 do horného radu portu JD v doske Zybo.

Krok 10: Zostavenie modulu PWM- generujte bitstream a spustite SDK

1. Na karte Project Navigator spustite Generate BitStream.

2. Exportujte hardvér: Súbor> Exportovať> Exportovať hardvér-> označte „zahrnúť bitový tok“-> OK 3. Spustite súpravu SDK: Súbor-> Spustiť súpravu SDK.

Krok 11: Zostavenie modulu PWM- vytvorte novú aplikáciu v súprave Xilinx SDK

Vytvorte novú aplikáciu:

Súbor> Nový> Projekt aplikácie -> Zadajte názov projektu -> Dokončiť

V programe Project Explorer by mali existovať tri priečinky.

V tomto prípade je „design_1_wrapper_hw_platform_0“priečinok, ktorý predtým exportoval Vivado. Axis_2_PWM_SDK_bsp je priečinok balíka podpory dosky. A Axis_2_PWM_SDK je náš hlavný priečinok projektu v SDK. Súbor „helloworld.c“môžete vidieť v priečinku „src“programu Axis_2_PWM_SDK, kde je hlavným súborom „helloworld.c“.

Krok 12: Zostavenie modulu PWM- prehľad programu Explorer (I)

Pozrime sa na niektoré súbory v programe Project Explorer. Najprv v priečinku „design_1_wrapper_hw_platform_0“otvorte súbor „system.hdf“. Tento súbor ukazuje mapu adries pre procesor ps7_cortex9 a bloky IP prítomné v našom návrhu.

Krok 13: Zostavenie modulu PWM- prehľad programu Explorer (II)

Potom skontrolujte súbor „include“a „libsrc“v priečinku „Axis_2_PWM_SDK_bsp“. Súbory knižnice nám tu umožňujú interakciu s hardvérovými perifériami bez „prehrávania“registrov.

Krok 14: Zostavenie modulu PWM- prehľad programu Explorer (III)

Prostredníctvom dokumentácie BSP je xtmrctr.h nájdený ako riadiaca knižnica časovača Xilinx súvisiaca s AXI Timer. Typicky by sme tu mohli nájsť požadovanú funkciu PWM. Ak si však prečítate dokumentáciu „tmrctr_v4_3“, ukáže sa, že ovládač v súčasnosti nepodporuje prevádzku zariadenia PWM. Vzhľadom na nedostatok funkcie PWM musíme našu funkciu PWM zabaliť pomocou sprievodcu produktmi xtmrctr.h a AXI Timer v2.0 LogiCORE IP.

Krok 15: Zostavenie modulu PWM- Zbaľte funkciu PWM (I)

Späť na hlavný súbor „helloworld.c“obsahuje nasledujúce hlavičkové súbory:

Krok 16: Zostavenie modulu PWM- Zbaľte funkciu PWM (II)

Definujte základné adresy dvoch AXI TImer prostredníctvom „xparameters.h“.

Krok 17: Zostavenie modulu PWM- Zbaľte funkciu PWM (III)

Vytvorte požadovanú funkciu PWM.

Duty_val: prevádza hodnotu stupňa na pracovný cyklus. PWM_Freq_Duty: nastavte požadovanú frekvenciu a pracovný cyklus na generovanie PWM. Tiež by malo byť priradené časové obdobie.

PWM_START: Priraďte adresu registra PWM a začnite generovať PWM.

PWM_STOP: priradenie adresy registra PWM a zastavenie generovania PWM.

Zvyšok demo kódu je uvedený v „helloworld.c“v „Axis_2_PWM_SDK“

Krok 18: Zostavenie modulu PWM- spustite ho

1. Naprogramujte FPGA pomocou SDK

- Pripojte Zybo Board cez USB port k PC.

- Nástroje Xilinx -> Program FPGA

2. Spustite program

Kliknite na ikonu „Spustiť“a rozbaľte ponuku -> Spustiť ako -> Spustiť na hardvéri

3. Terminál SDK

- Otvorte terminál SDK -> Pripojiť k sériovému portu -> OK

- Spustite program. Ak sa demo kód úspešne spustí, mali by ste vidieť „Inicializácia bola dokončená!“na termináli SDK.

Krok 19: Spracovanie streamovaného videa na zariadení Digilent ZYBO s OV7670

Priložený kompletný archívny súbor.

Krok 20: Kompletný blokový diagram

Toto ukazuje kompletný diagram všetkých pripojení a blokov IP v projekte

Krok 21: Pripojte OV7670 k ZYBO

Vytvorte spojenie a zapojte modul ov7670 do ZYBO Pmods

Dátový Pmod je Pmod D

Ovládací Pmod je Pmod C.

Okrem toho pripojte PmodCON3 a serva podľa pokynov v prvej polovici tohto tutoriálu

Krok 22: Vytvorte návrh bloku

V aplikácii Flow Navigator kliknite na „Vytvoriť návrh bloku“a potom kliknite na tlačidlo OK.

Krok 23: Pridajte súbory VHDL pre ovládanie a snímanie kamery OV7670

Pridajte do projektu súbory VHDL pripojené k tomuto kroku

Krok 24: Pridajte súbor obmedzení

Pridajte priložený súbor obmedzení do svojho projektu.

Krok 25: Pridajte IP Repo pre HLS IP

Vezmite priložený súbor Zip a rozbaľte ho do nového priečinka s podobným názvom v novom adresári (priečinku) s názvom „HLS_repo“.

Pridajte do svojho projektu úložisko IP tak, že prejdete do katalógu IP a pravým tlačidlom myši vyberiete položku „Pridať úložisko …“

Prejdite do svojho adresára „HLS_repo“a vyberte ho.

Voliteľné: Vytvorte si blok spracovania videa HLS pre seba!

Krok 26: Pridajte moduly a IP

Pridajte moduly ov7670_axi_stream_capture, debounce a ov7670_controller do blokového diagramu kliknutím pravým tlačidlom na pozadie a výberom položky „Pridať modul …“

Podobne pridajte adresy IP:

- HLS_Video_Track

- Zápis do vyrovnávacej pamäte videa

- Čítanie vyrovnávacej pamäte video rámca

- Ovládač časovania videa

- Výstup AXI4-stream na video

- 3 „Plátok“

- Konštantný

- 2 časovača AXI

Krok 27: Nastavenia konfigurácie IP

Ako je znázornené na obrázkoch

Krok 28: Pridajte a nakonfigurujte blok IP IP

Pridajte procesorový systém ZYNQ7 do blokového diagramu

upraviť konfiguráciu:

-

Konfigurácia PS-PL

-

HP

- Povoliť S HP 0

- Povoliť S HP 1

-

-

Konfigurácia hodín

-

Látkové hodiny PL

- FCLK_0 pri 100 MHz

- FCLK_1 pri 25 MHz (OutputClock)

- FLCK_2 pri 35 MHz (<= 50 MHz) (CameraClock)

-

Krok 29: Časť 1. Zostavenie modulu PWM pre servomotory

Vyveďte axi_timer_0 pwm0 do nového výstupného portu pwm_Xaxis

Vyveďte axi_timer_1 pwm0 do nového výstupného portu pwm_Zaxis

Krok 30: Pripojenia bočného vstupu videa (zvýraznené)

Správne pripojte bloky IP na strane vstupu videa

(* tieto pripojenia by mali byť vytvorené výberom správnych možností počas automatizácie pripojení) „aclk“z axi_stream_capture ide na:

- ap_clk na zápis do vyrovnávacej pamäte video rámca

- ap_clk v bloku spracovania toku videa HLS

- *aclk na AXI smartconnect IP z vyrovnávacej pamäte video rámca zapísať do S_AXI_HP0

- *aclk zodpovedajúci kanálom AXI Interconnect IP pre kanály S_AXI bloku spracovania videa HLS a vyrovnávacia pamäť video rámca zapísať S_AXI_HP0_ACLK do bloku PS

Signál toku videa je jednoducho zapojený do série od zachytávacieho bloku k pamäťovému rozhraniu Zynq.

- Video prechádza z bloku zachytávania do bloku spracovania HLS.

- Spracované video z bloku HLS prejde do bloku na zápis do vyrovnávacej pamäte rámcov.

- *Blok zápisu do vyrovnávacej pamäte rámca sa pripája k rozhraniu HP0 v bloku Zynq PS.

- Signál m_axis_tuser z výstupu zachytávacieho bloku je ručne prepojený so vstupným signálom video_in_TUSER na bloku spracovania HLS a signálom ap_start v tom istom bloku.

Signál TUSER (tuser) používa protokol toku videa AXI na označenie začiatku rámca videa. AP_Start hovorí bloku HLS, aby spustil spracovanie. Používame teda tuser na spustenie bloku HLS na spracovanie každého rámca tak, ako prichádza. Pri pripájaní jedného signálu zbernice a jeho oddelení týmto spôsobom je potrebné pripojiť aj normálny koncový bod zvyšku zbernice. Vivado predpokladá, že ak ručne pripájate signál, chcete odpojiť to, k čomu by sa bežne pripájal.

Konfiguračné nastavenia IP blokov:

Zápis do vyrovnávacej pamäte video rámca:

Formáty videa: RGB8

1 vzorka za hodiny Max. Stĺpce: 1280 (> = 640) Max. Riadky: 960 (> = 480) Max. Šírka dát: 8

Krok 31: Pripojenia k OV7670

Na bloku ov7670_axi_stream_capture

- Vykonajte všetky vstupy externé (kliknite pravým tlačidlom myši na špendlík a vyberte ho z ponuky alebo kliknite ľavým tlačidlom myši-> ctrl+T)

- Mená nechajte tak, ako sú

Na bloku ov7670_controller

- Vykonajte všetky výstupy bloku externé

- Premenujte port config_finished na led0

- pripojte clk k CameraClock (<= 50 MHz) (FCLK_2)

Na debounce bloku

- pripojte vstup button1 k externému vstupnému portu s názvom btn0

- pripojte out1 k linke opätovného odoslania v bloku IP ov7670_controller

- pripojte vstup button2 k externému vstupnému portu s názvom btn3

- pripojte výstup out2n k vstupu ext_reset_in na adrese IP procesora resetovania systému pre doménu hodín záznamu videa. (*Možno to bude potrebné urobiť po vygenerovaní adresy IP*)

- pripojte clk k CameraClock (<= 50 MHz) (FCLK_2)

Krok 32: Pripojenia na strane výstupu videa

Pripojenia pre bloky Video Timing Controller (VTC), AXI4-Stream to Video Out a rezy

- Na vid_io_out_clk a VTC clk použite hodiny 25 MHz (FCLK_1)

- Na aclk na výstupe AXI4-Stream-Video použite hodiny 100MHz (FCLK_0)

- vtiming_out až vtiming_in

- Čítanie vyrovnávacej pamäte video rámca m_axis_video prejde na AXI4-Stream na výstup videa video_in

- vtg_ce ide do gen_clken

- Spojte VTC clken, aclken, vid_io_out_ce s konštantným doutom [0: 0]

- Priveďte vid_hsync a vid_vsync na externé výstupné porty vga_hs, respektíve vga_vs. (bez obrázku)

Plátky:

-

Plátky by mali byť nastavené tak, ako je to znázornené na priložených obrázkoch

- premenujte bloky na slice_red, slice_green a slice_blue

- nastavte rozsahy rezov, ako je znázornené na obrázkoch, podľa názvu bloku

- pripojte každý výstup segmentu k výstupu externého portu, ako je znázornené na obrázku.

- vid_data [23: 0] sa pripája k vstupom pre každý plátok (Din [23: 0])

Krok 33: Spustite automatizáciu blokov a pripojení

Spustením automatizácie blokov spojíte veci z bloku ZYNQ7 PS. Ako ukazuje obrázok.

Spustením automatizácie pripojenia vytvoríte všetky IP prepojenia. Venujte veľkú pozornosť všetkým možnostiam na každom obrázku.

Na debounce bloku pripojte out2n k vstupu do domény s hodinovým záznamom videa. Procesor Reset systému ext_reset_in.

Krok 34: Vytvorte obalový program HDL

Vytvorte obal HDL pre svoj návrh bloku.

Nastavte ho ako horný modul.

Krok 35: Generujte bitstream, exportujte hardvér do SDK, spustite SDK z Vivado

Do exportu určite zahrňte bitový tok.

Generovanie bitového toku môže trvať veľmi dlho.

Potom spustite SDK

Krok 36: SDK (žiadne FreeRTOS)

Táto verzia robí všetko bez použitia FreeRTOS, pričom pekne kondenzuje kód.

Vytvorte samostatný BSP na základe hardvérového návrhu. Predvolené možnosti by mali byť v poriadku. Uistite sa, že boli vygenerované zdroje BSP.

Vytvorte aplikáciu podľa obrázka. (prázdna aplikácia)

Odstráňte automaticky generovaný hlavný súbor a importujte priložené súbory.

Krok 37: Implementácia FreeRTOS

Táto verzia používa FreeRTOS. Vytvorte FreeRTOS901 BSP na základe návrhu hardvéru. Predvolené možnosti by mali byť v poriadku. Uistite sa, že boli vygenerované zdroje BSP.

Vytvorte aplikáciu podľa obrázka. (prázdna aplikácia)

Odstráňte automaticky generovaný hlavný súbor a importujte priložené súbory.

Krok 38: Pokyny na použitie

Spustenie tohto projektu je trochu zložité. Postupujte podľa uvedených pokynov.

Uistite sa, že váš ZYBO po zapnutí nič nenabíja. To znamená, že kontrolka Hotovo by sa nemala rozsvietiť. Jedným zo spôsobov, ako to urobiť, je nastaviť prepojku zdroja zavádzania na JTAG.

Otvorte projekt (FreeRTOS alebo nie), ktorý chcete programovať zo sady SDK

- Zapnite ZYBO. Kontrolka Hotovo by sa nemala rozsvietiť.

- Naprogramujte FPGA pomocou bitového súboru. Kontrolka Hotovo by sa mala rozsvietiť. Led0 by sa nemalo rozsvietiť.

- Spustite kód (ak to robíte, nezabudnite prejsť za štartovací bod).

V tomto mieste by ste mali získať výstup na svojom displeji VGA.

Reštartovanie (ak sa vyskytne chyba alebo čokoľvek): rýchlo klepnite na tlačidlo PS-SRST alebo vypnite a znova zapnite ZYBO. Pokračujte od kroku 2.

Zastavenie procesora pomocou debuggera spôsobí, že kamera bude držať pozíciu, namiesto toho, aby sa pohybovala. Stream videa bude aj tak pokračovať.

Krok 39: Referencie a odkazy

Referenčné príručky a dokumentácia k Xilinx:

- PG044 - Výstup AXI - stream na video

- PG278 - vyrovnávacia pamäť rámca videa na čítanie/zápis

Ďalšie odkazy:

- Lauriin blog - vstup VDMA

- Lauriho blog - výstup OV7670 na VGA pomocou BRAM

- Wiki Hamsterworks, Mike Fields, pôvodný zdroj kódu OV7670

- Technický list so základnými špecifikáciami načasovania

Odporúča:

Rýchlosť a smer otáčania a smeru motora DC Arduino pomocou potenciometra a tlačidiel: 6 krokov

Rýchlosť a smer otáčania a smeru jednosmerného motora Arduino pomocou potenciometra a tlačidiel: V tomto návode sa naučíme, ako pomocou ovládača L298N DC MOTOR CONTROL a potenciometra ovládať rýchlosť a smer jednosmerného motora dvoma tlačidlami. Pozrite si ukážkové video

Robot Arduino so vzdialenosťou, smerom a stupňom otáčania (východ, západ, sever, juh) ovládaný hlasom pomocou modulu Bluetooth a autonómnym pohybom robota .: 6 krokov

Robot Arduino so vzdialenosťou, smerom a stupňom otáčania (východ, západ, sever, juh) ovládaný hlasom pomocou modulu Bluetooth a pohybu autonómneho robota .: Tento návod vysvetľuje, ako vyrobiť robot Arduino, ktorý je možné pohybovať v požadovanom smere (dopredu, dozadu (Vľavo, Vpravo, Východ, Západ, Sever, Juh) požadovaná vzdialenosť v centimetroch pomocou hlasového ovládania. Robota je možné pohybovať aj autonómne

Kamera s diaľkovým ovládaním: 5 krokov (s obrázkami)

Fotoaparátová bábika na diaľkové ovládanie: Niečo veľmi praktické, čo by ste mohli mať pri natáčaní videa, je bábika. Je ešte chladnejšie, ak je napájané, a jeho diaľkové ovládanie je čerešnička na torte. Tu vyrábame bábiku na diaľkové ovládanie za menej ako 50 dolárov (v čase písania tohto článku)

Mechanizmus otáčania a nakláňania pre časozbery DSLR: 7 krokov (s obrázkami)

Mechanizmus otáčania a nakláňania pre časozbery DSLR: Ležalo tu niekoľko krokových motorov a naozaj som ich chcel použiť na výrobu niečoho chladného. Rozhodol som sa, že pre svoju kameru DSLR vyrobím systém Pan and Tilt, aby som mohol vytvárať skvelé časové oneskorenia. Položky, ktoré budete potrebovať: 2x krokový motor -http

Nabodujte svoj raketomet USB ako „automatické zameriavanie automatického otáčania!“: 6 krokov

Hackujte svoj odpaľovač rakiet USB do „Automatického zameriavania autoturretu!“: Ako prinútite svoj odpalovač rakiet USB, aby mieril sám. Tento návod vás naučí premieňať odpaľovacie zariadenia USB na automatické otáčanie, ktoré bude nachádzať ciele IR a zameriavať ich. (Ospravedlňujeme sa iba za IR ciele)